# IMPROVING ENERGY AND PERFORMANCE OF DATA CACHE ARCHITECTURES BY EXPLOITING MEMORY REFERENCE CHARACTERISTICS

by

## Hsien-Hsin Sean Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2001

## Doctoral Committee:

Assistant Professor Gary S. Tyson, Chair Assistant Professor Todd M. Austin Professor Richard B. Brown Professor Edward S. Davidson Assistant Professor Steven K. Reinhardt

## ABSTRACT

# IMPROVING ENERGY AND PERFORMANCE OF DATA CACHE ARCHITECTURES BY EXPLOITING MEMORY REFERENCE CHARACTERISTICS

by Hsien-Hsin Sean Lee

Chairperson: Gary S. Tyson

Minimizing power, increasing performance, and delivering effective memory bandwidth are today's primary microprocessor design goals for the embedded, high-end and multimedia workstation markets. In this dissertation, I will discuss three major data cache architecture design optimization techniques, each of which exploits the data memory reference characteristics of the applications written in high-level languages. Through a better understanding of the memory reference behavior, we can design a system that executes at higher performance, while consuming less energy, and delivering more effective memory bandwidth.

The first part of this dissertation presents an in-depth characterization of data memory references, including analysis of semantic region accesses and behavior of data stores. This analysis leads to a new organization of the data cache hierarchy called Region-based Cachelets. Region-based Cachelets are capable of improving memory performance of embedded applications while significantly reducing dynamic energy consumption, resulting in a 50% to 70% improvement in energy-delay product efficiency using this approach.

Following this, I will discuss a new cache-like structure, the Stack Value File (or SVF), which boosts performance of general purpose applications by routing stack data references to a separate storage structure optimized for the unique characteristics of the stack reference substream. By utilizing a custom structure for stack references, we are able to increase memory level parallelism, reduce memory latency, and reduce off-chip memory activity. The performance can be improved by 24% by implementing an 8KB SVF for a processor with a dual-ported L1 cache.

Finally, I will address memory bandwidth issues by proposing a new write policy called Eager Writeback which can effectively improve overall system performance by shifting the writings of dirty cache lines from on-demand to times when the memory bus is less congested. It lessens the criticality of on-demand misses and improves performance by 6% to 16% for the 3D graphics geometry pipeline.

To my parents, Mr. C.-H. Lee and Mrs. C.-H. Liko.

## ACKNOWLEDGEMENTS

This dissertation seemed to be an endless pilgrimage for me in the beginning. Without mentors and friends, I could not reach my destination. It is my privilege to have Gary Tyson as my thesis advisor. Gary shares with me his many research ideas, presentation skills, friendship, and house building tips, not only makes my Ph.D. research fruitful but also enjoyable. I am greatly indebted to Ed Davidson, who guided me into the dome of computer architectures in 1993. He also served as my first research advisor and provided me a research assistantship from 1993 to 1995. I also want to express my maximum gratitude to my former manager also a principal architect at Intel Corporation, Vladimir Pentkovski, who taught me how to be skeptical of anything we read and how to become a good researcher. I thank Todd Austin, Richard Brown, and Steven Reinhardt for serving in my thesis committee and providing many precious comments in my work. I also thank Matt Farrens and Chris "CJ" Newburn for their insightful discussions during our cooperation. I thank Jesse Fang for the Intel Fellowship during my last year at Michigan.

There are many friends at Michigan who continue to keep me sane from various stages of my wonderful two-episode doctorate journey. People from episode one (1992 to 1995), Chih-Chieh Lee, Chien-Chang Liu, Jude Rivers, Tien-Pao Shih, I-Cheng Chen, Perry Wang, John-David Wellman, Chuan-Hua Chang, Hung-Kuei Ku, Jia-Jang Liou, Eric Hao, Eric Boyd, Po-Yung Chang, Waleed Meleis, Alexandre Eichenberger, Karen Tomko, Gheith Abandah and Shih-Hao Hung. People from episode two (1999-2001): Viji Srinivasan, Stevan Vlaovic, Murali Annavaram, Mikhail Smelyanskiy, Suhwan Kim, Wei-Fen Lin, Brian Hutsell, Nagarajan Kandasamy, Ramu Pyreddy, Lisa Wu, Xun Liu, Shao-Lun Li and Shuo-Hung Hsu.

Special thanks to my college roommates Shyh-Kang Chang and Chi-Wei Wang, who convinced me to abandon my original plan of going to Wisconsin and join their adventures at Michigan in order to share an apartment again.

I thank all of my brilliant Intel friends including Emile Hsieh, Wen-Hsun Han, Youfeng Wu, Shih-Wei Liao, Hong Wang, Paul Zagacki, Chung-Chi Wang, Steve Tsai, Trung Diep, Deep Buch and Mike Dwyer, whom I learned a lot from. In particular, my best friend and also my closest partner in the entire Pentium III development, Hsien-Cheng "Emile" Hsieh, who passed away just 3 days after I finished my oral defense and left me so much grief and regret not even having a chance to share my accomplishment with him. Emile, the work we had done together will be the best treasure of my life and you will always live in my heart.

I thank my high school and college buddies, Bin-Hung Lin, Yung-Fa Chou, Chien-Liang Lin, Hao-Chao Hong, Hsiao-Tzu Ni, Wan-Thai Hsu and Tsung-Lin Cheng, who give me hope and inspiration constantly and galvanize me with their wild ideas once a while.

Finally, I would like to thank my family for their unconditional support. I thank my lovely wife Esther Liu, how lucky I am to have you with me for all these years. I thank my younger sister Hui-Yin Lee who always cheers me up during my ups and downs. I thank my parents Ching-Hsiung Lee and Chung-Hua Liko for giving me love and providing whatever I need since day one.

# TABLE OF CONTENTS

| DEDICATIO                   | <b>N</b>                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLE                    | DGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LIST OF FIG                 | URES vi                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LIST OF TAI                 | BLES ix                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LIST OF AP                  | PENDICES                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTERS                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1 INTR<br>1.1<br>1.2        | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2 EXPE<br>2.1<br>2.2        | CRIMENTAL FRAMEWORK       4         Processor Simulator and Tool Suites       4         Benchmarks       5         2.2.1 SPEC       5         2.2.2 Mediabench       5         2.2.3 X Benchmark       7         2.2.4 3D Geometry Pipeline       7         2.2.5 Streaming Kernel       9                                                                                                                                                            |

| 3 MEM 3.1 3.2  3.3  3.4 3.5 | ORY REFERENCE CHARACTERIZATION 11 Virtual Memory Space Partitioning 11 Memory Reference Distribution 12 3.2.1 Distribution of Memory Instructions 12 3.2.2 Distribution of Data Cache Occupancy 12 Analysis of Regional Reference Characteristics 14 3.3.1 Weighted Reference Distance 14 3.3.2 Unique Memory Block References by Region 16 3.3.3 Information Content of Cache Frame Addresses 17 Behavior of Cache Line Writes 19 Chapter Summary 25 |

| 4 LOW<br>4.1<br>4.2<br>4.3  | ENERGY REGION-BASED CACHELETS 26 Cache Structures and Power Dissipation 27 4.1.1 Overview of Cache Structures 27 4.1.2 Power Models 27 4.1.3 Power Modeling in Cache Structures 28 Locality of Data Cache Regions 29 Region-based Cachelets 36                                                                                                                                                                                                        |

|   | 4.4        | Simulation Framework                                                              |

|---|------------|-----------------------------------------------------------------------------------|

|   |            | 4.4.2 Energy-Delay Product Metric                                                 |

|   | 4.5        | Simulation Results and Analysis                                                   |

|   |            | 4.5.1 Comparisons with Baseline Design                                            |

|   |            | 4.5.2 Exploiting Design Space of Region-based Cachelets                           |

|   |            | 4.5.3 Combining a Filter Cache and Region-based Cachelets 39                      |

|   |            | 4.5.4 Design Options with a Filter Cache                                          |

|   | 4.6        | Related Work                                                                      |

|   | 4.7        | Chapter Summary                                                                   |

| 5 | HIGH-      | PERFORMANCE STACK VALUE FILE                                                      |

|   | 5.1        | Stack Reference Characteristics                                                   |

|   | 5.2        | Motivation for Stack Value File Design                                            |

|   | -          | 5.2.1 Contiguity                                                                  |

|   |            | 5.2.2 Stack Depth Variations and Locality                                         |

|   | 5.3        | Stack Value File Design                                                           |

|   | 5.5        | 5.3.1 Morphing Stack-Pointer Based References                                     |

|   |            | 5.3.2 Stack Memory Reference Disambiguation                                       |

|   |            | 5.3.3 SVF Status Bits                                                             |

|   |            | 5.3.4 Accesses Outside Defined Scope                                              |

|   |            | <u> </u>                                                                          |

|   | F 4        |                                                                                   |

|   | 5.4        | Experimental Configuration                                                        |

|   | 5.5        | Performance Evaluation and Design Trade-Offs                                      |

|   |            | 5.5.1 Improving Cache Bandwidth, Latency and ILP 61                               |

|   |            | 5.5.2 Hierarchical Performance Analysis                                           |

|   |            | 5.5.3 SVF vs. Stack Cache                                                         |

|   |            | 5.5.4 Interlock Stall Overheads                                                   |

|   |            | 5.5.5 Memory and SVF Ports                                                        |

|   | 5.6        | Related Work                                                                      |

|   | 5.7        | Chapter Summary                                                                   |

| 6 |            | TENT BANDWIDTH UTILIZATION USING AN EAGER WRITEBACK                               |

|   |            | E                                                                                 |

|   | 6.1        | Caches and Memory Subsystem                                                       |

|   | 6.2        | Eager Writeback                                                                   |

|   |            | 6.2.1 Overview                                                                    |

|   |            | 6.2.2 Design Issues in Eager Writeback Caches                                     |

|   | 6.3        | Simulation Framework                                                              |

|   | 6.4        | Simulation Results and Analysis                                                   |

|   |            | 6.4.1 Spec95 Benchmarks                                                           |

|   |            | 6.4.2 Analysis of 3D Geometry Pipeline                                            |

|   |            | 6.4.3 Streaming Kernel                                                            |

|   | 6.5        | Related Work                                                                      |

|   | 6.6        | Chapter Summary                                                                   |

| 7 | CONC       | LUSIONS AND FUTURE DIRECTIONS                                                     |

| • | 7.1        | Thesis Summary                                                                    |

|   | 1.1        | 7.1.1 Memory Reference Characterization                                           |

|   |            | v                                                                                 |

|   |            | 7.1.2 Region-based Cachelets                                                      |

|   |            | 7.1.3 Stack Value File Design                                                     |

|   | <b>7</b> 0 | 7.1.4 Eager Writeback Cache                                                       |

|   | 7.2        | Future Directions         94           7.2.1         Cache Port Design         94 |

|   |            |                                                                                   |

| 7.2.2         | Energy Consumption in the Stack Value File | 94 |

|---------------|--------------------------------------------|----|

| 7.2.3         | Heap Object Management                     | 94 |

| APPENDICES    |                                            | 95 |

| BIBLIOGRAPHY. |                                            | 03 |

# LIST OF FIGURES

| Figure |                                                                                                            |    |

|--------|------------------------------------------------------------------------------------------------------------|----|

| 2.1    | Algorithm of the mini-geometry kernel                                                                      | 8  |

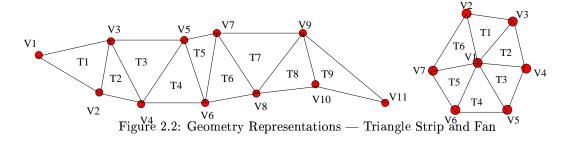

| 2.2    | Geometry Representations — Triangle Strip and Fan                                                          | 8  |

| 2.3    | Geometry Processing Loop Structure                                                                         | 9  |

| 2.4    | Algorithm of the Streaming Kernel                                                                          | 9  |

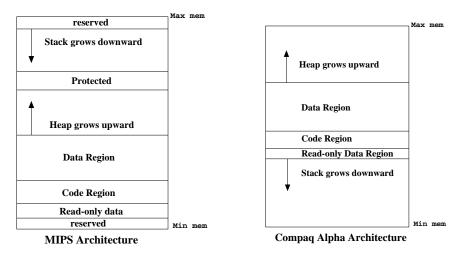

| 3.1    | Run-time Memory Subdivision for MIPS and Compaq Alpha Architectures                                        | 11 |

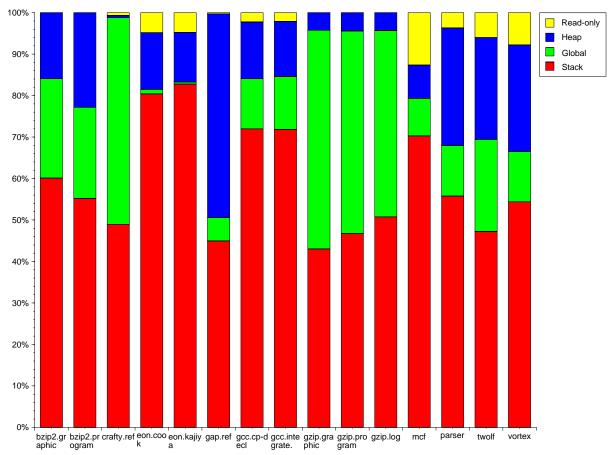

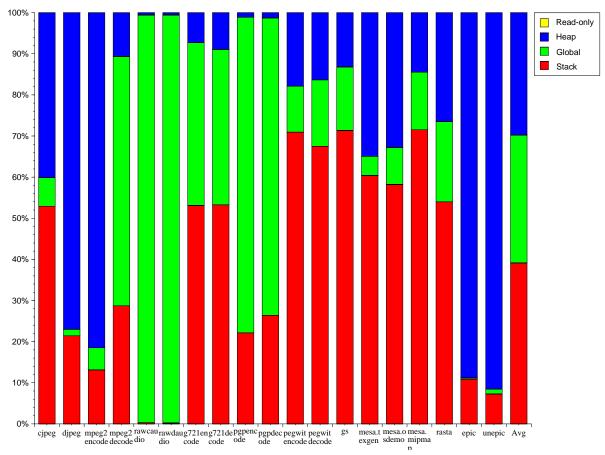

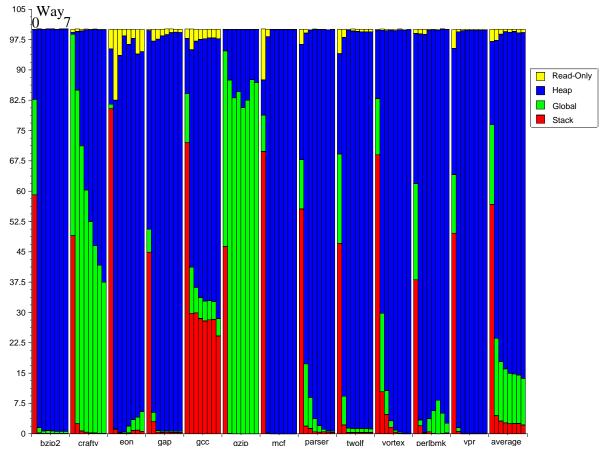

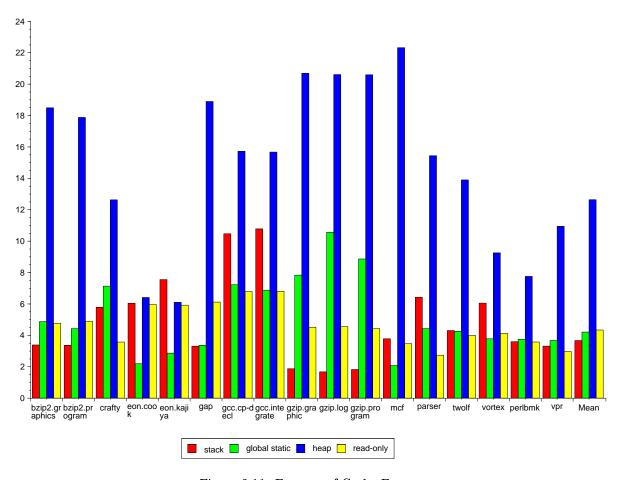

| 3.2    | Percentage of Memory Access Regions for SPECint2000                                                        | 13 |

| 3.3    | Percentage of Memory Access Regions for Mediabench                                                         | 14 |

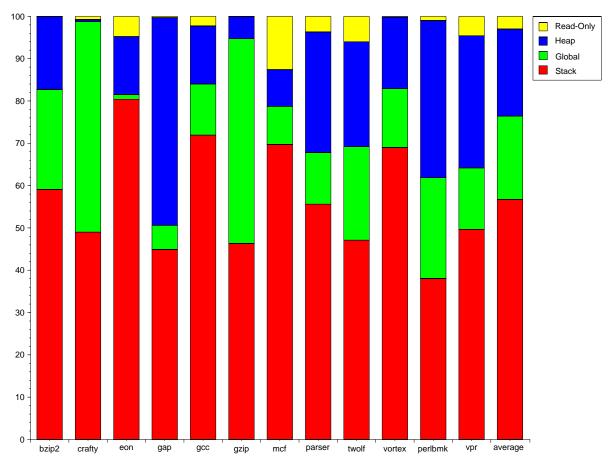

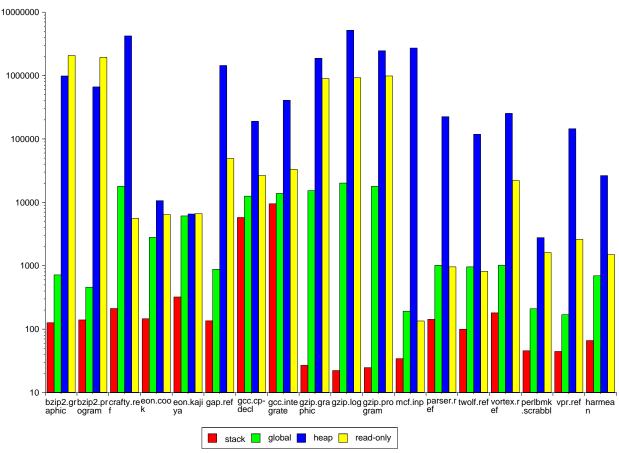

| 3.4    | Data Occupancy Ratios in Each Region for a Direct-Mapped 16KB Cache                                        | 15 |

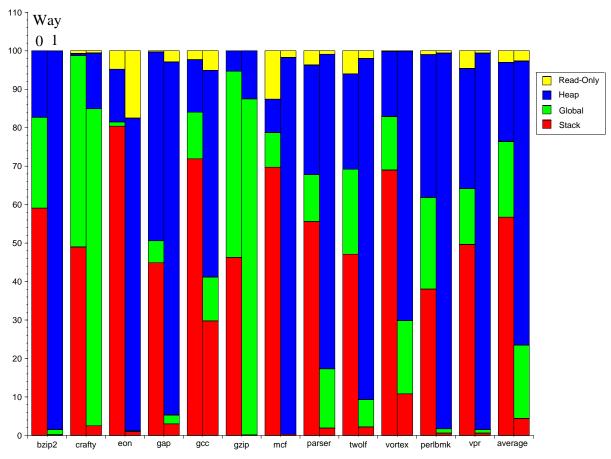

| 3.5    | Data Occupancy Ratios in Each Region for a 2-way 32KB Cache                                                | 16 |

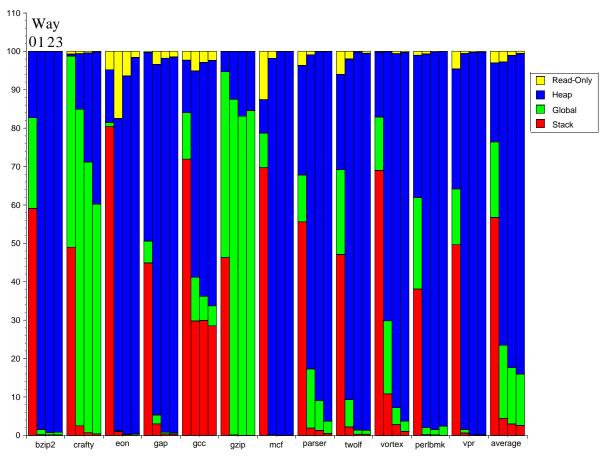

| 3.6    | Data Occupancy Ratios in Each Region for a 4-way 64KB Cache                                                | 17 |

| 3.7    | Data Occupancy Ratios in Each Region for an 8-way 128KB Cache                                              | 18 |

| 3.8    | Weighted Reference Distance of Cache Lines by Regions                                                      | 19 |

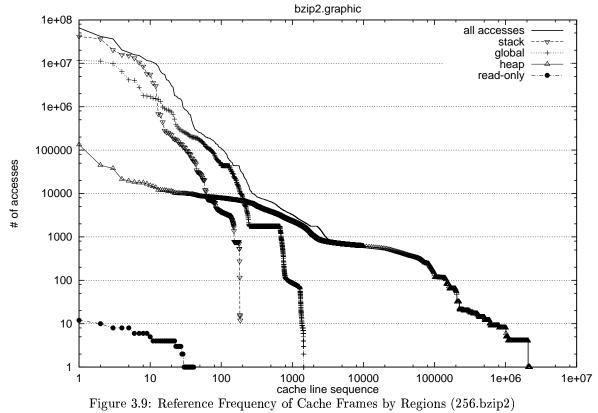

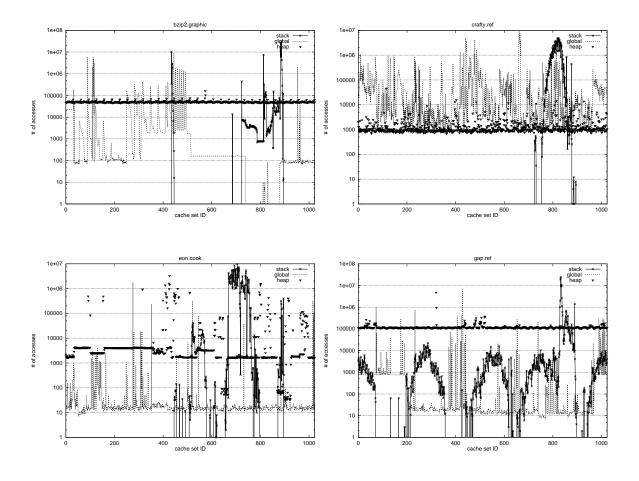

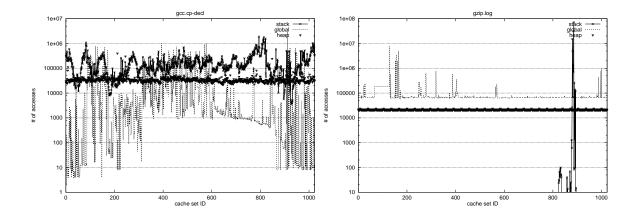

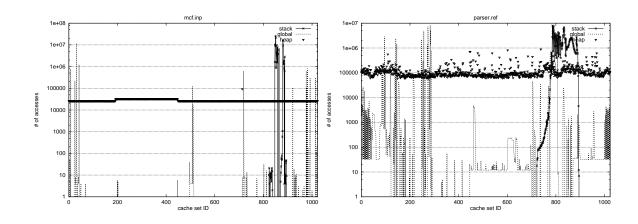

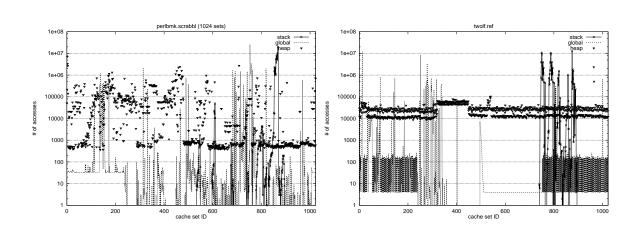

| 3.9    | Reference Frequency of Cache Frames by Regions (256.bzip2)                                                 | 20 |

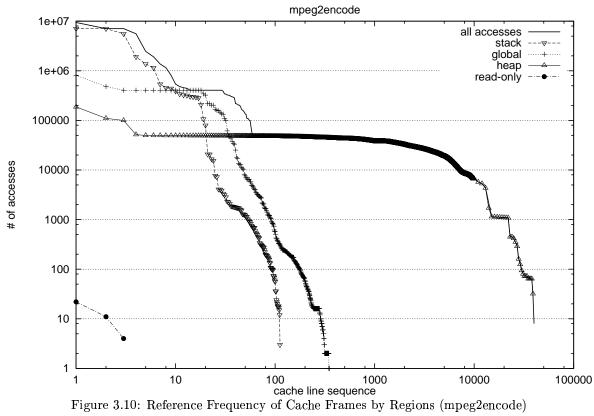

| 3.10   | Reference Frequency of Cache Frames by Regions (mpeg2encode)                                               | 20 |

| 3.11   | Entropy of Cache Frames                                                                                    | 21 |

| 3.12   | Expected Capacity Ratio of Two Caches                                                                      | 21 |

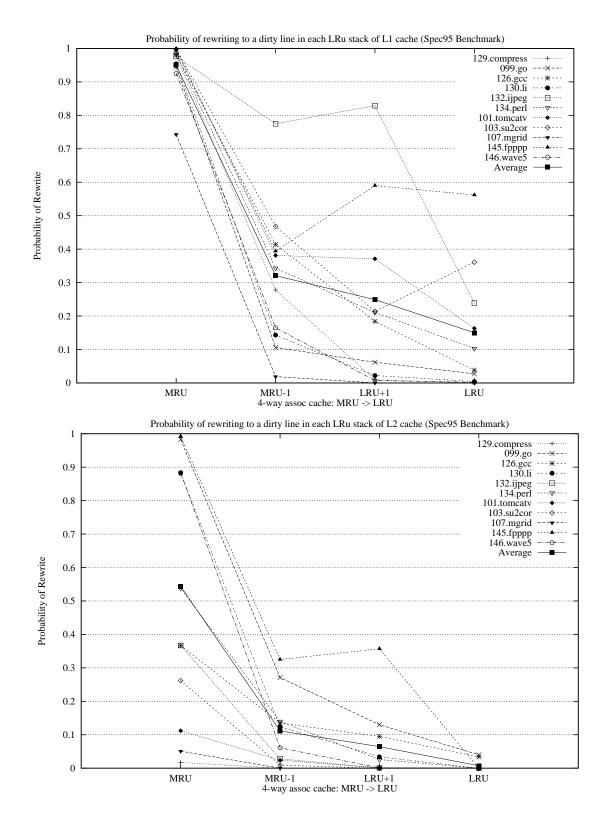

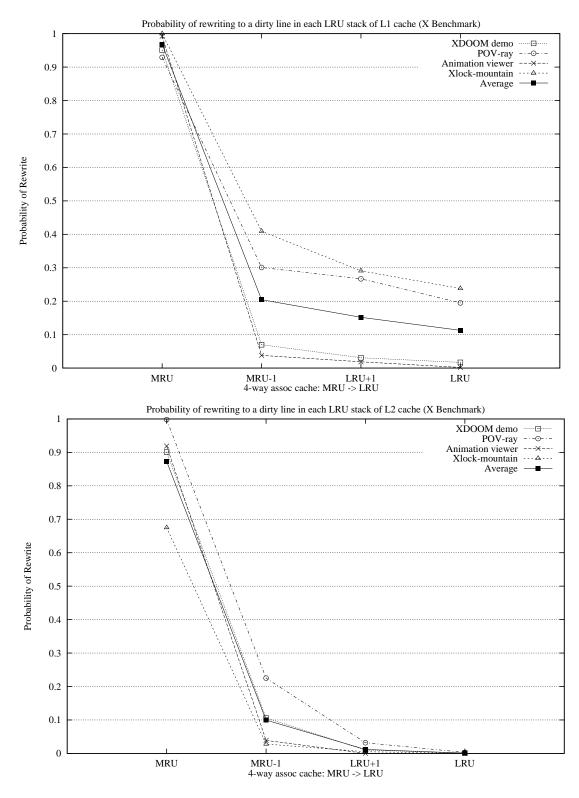

| 3.13   | Probability of writing to a dirty line in each LRU stack of L1 and L2 caches (SPEC95)                      | 23 |

| 3.14   | Probability of writing to a dirty line in each LRU stack of L1 and L2 caches (X                            |    |

|        | $\operatorname{benchmark})$                                                                                | 24 |

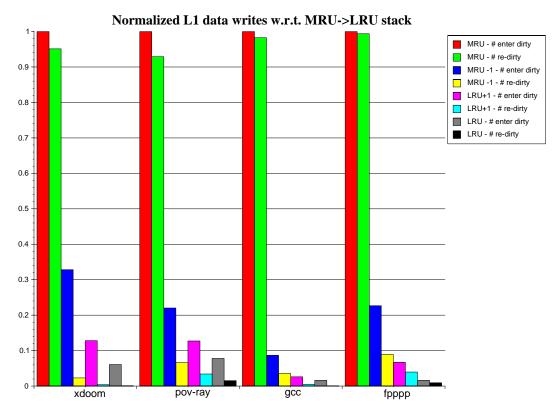

|        | Normalized number of writes and rewrites to a dirty line in each MRU-LRU stack .                           | 25 |

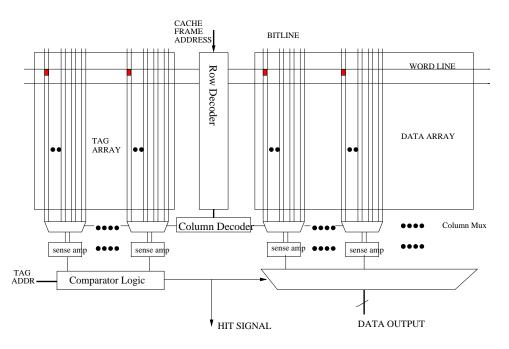

| 4.1    | Cache Memory Organization                                                                                  | 27 |

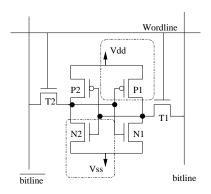

| 4.2    | A 6-transistor CMOS SRAM cell                                                                              | 28 |

| 4.3    | Average Life Span of Cache Lines by Regions for Mediabench                                                 | 30 |

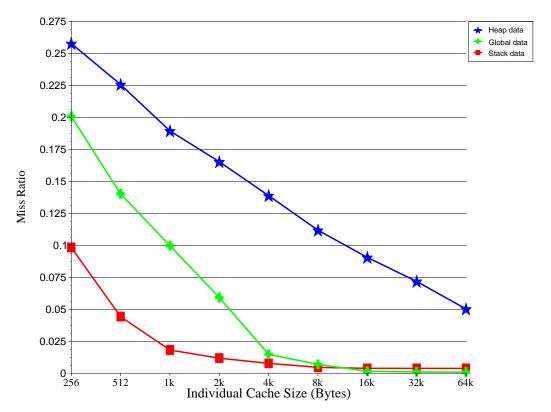

| 4.4    | Average Memory Region Miss Rates for Mediabench                                                            | 31 |

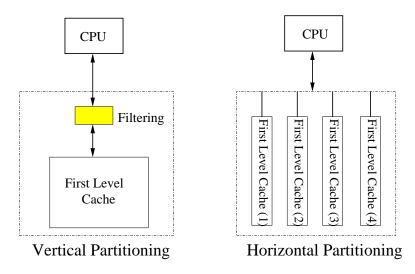

| 4.5    | Low-power Cache Partitioning Scheme                                                                        | 31 |

| 4.6    | Region-based Cachelets                                                                                     | 32 |

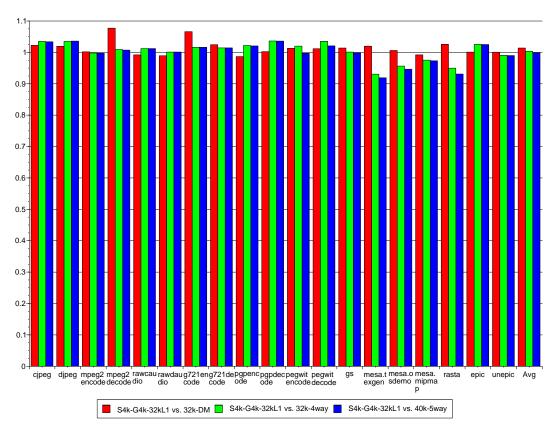

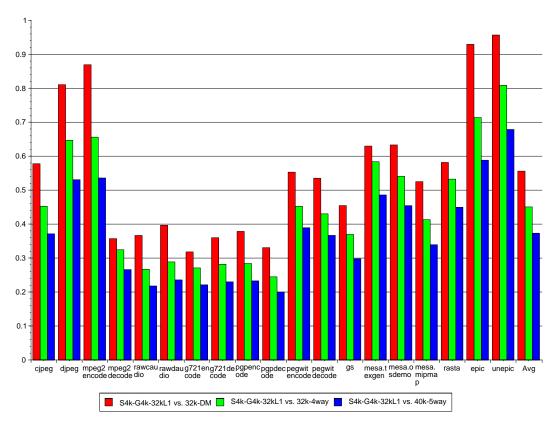

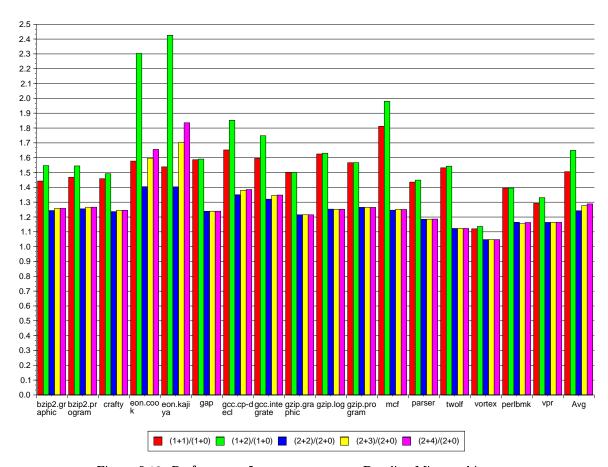

| 4.7    | Performance Comparison of Machines with Region-based Cachelets                                             | 35 |

| 4.8    | Power Dissipation Comparison of Machines with Region-based Cachelets                                       | 36 |

| 4.9    | Energy-Delay Product Comparison of Machines with Region-based Cachelets                                    | 37 |

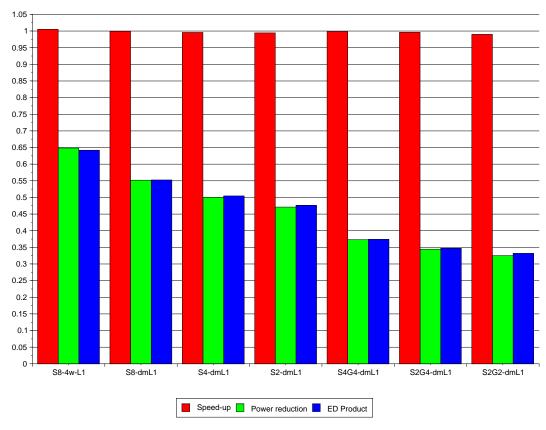

| 4.10   | Average Performance, Power and EDP for Different Region-based Cachelets Machines (Baseline: 5-way 40KB L1) | 38 |

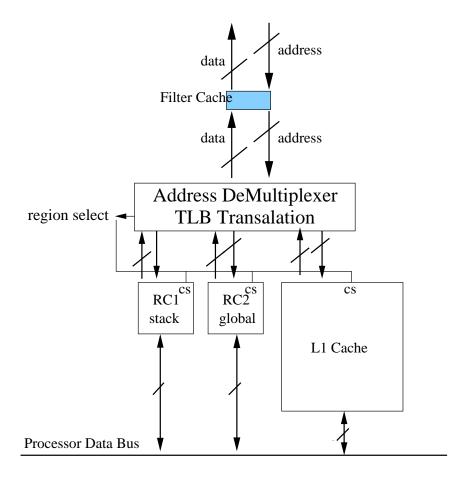

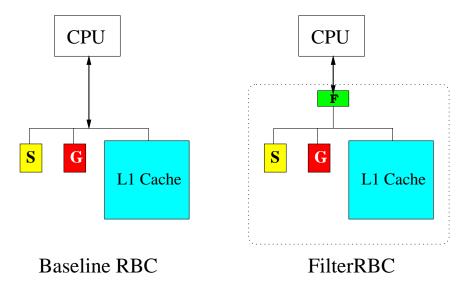

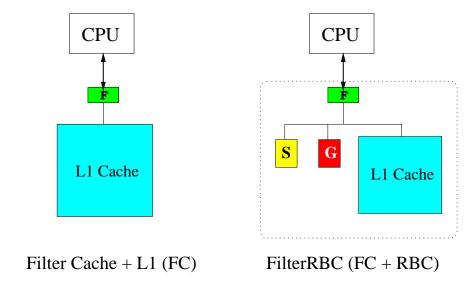

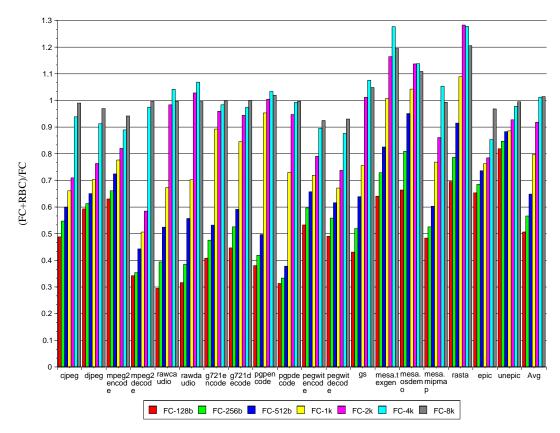

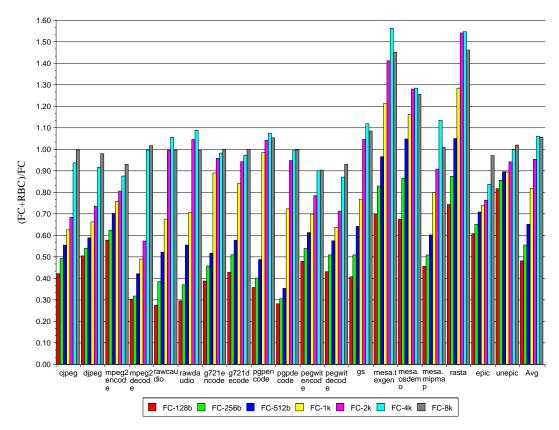

| 4.11   | Combining Filter Cache with Region-based Cachelets                                                         | 39 |

|        | Region-based Cachelets versus a Combined Filter Cache with Region-based Cachelets                          | 40 |

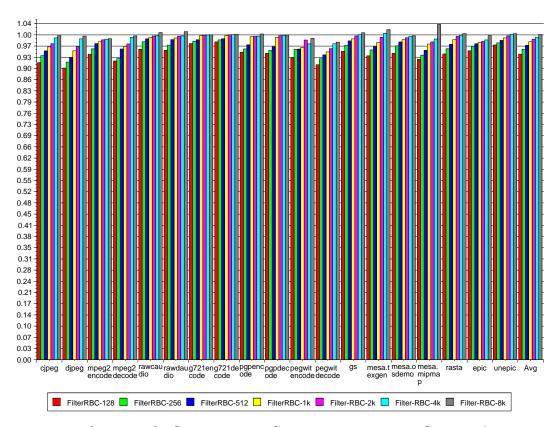

|        | Performance of a Combined Filter Cache with Region-based Cachelets (Baseline: S4k-                         |    |

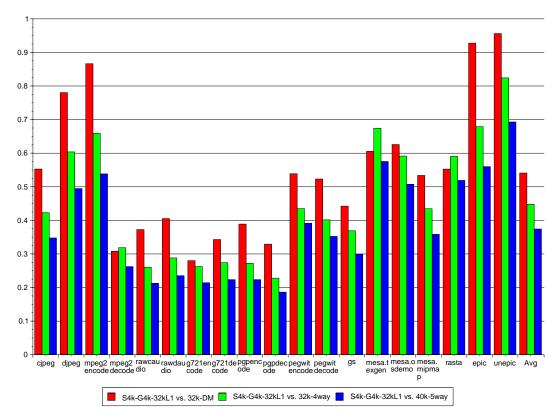

|        | G4k-32K with a 512KB L2 = 1.0) $\dots$                                                                     | 41 |

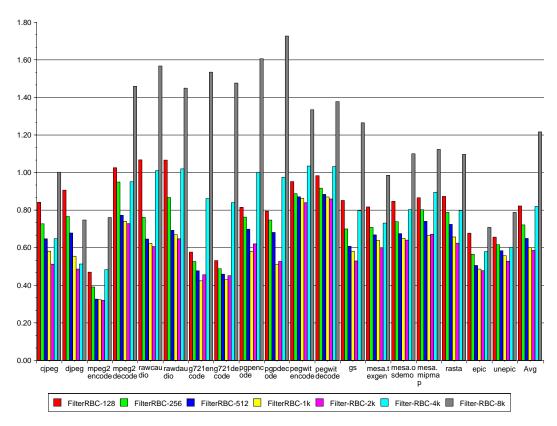

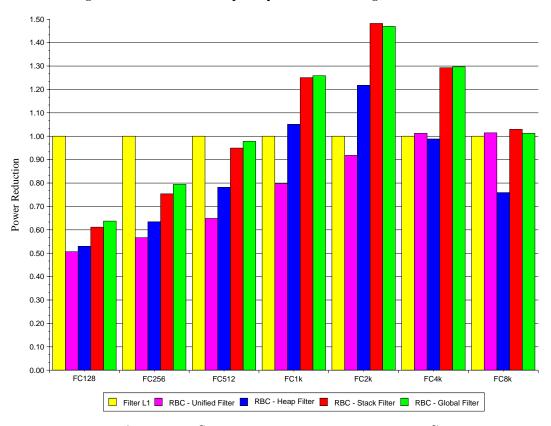

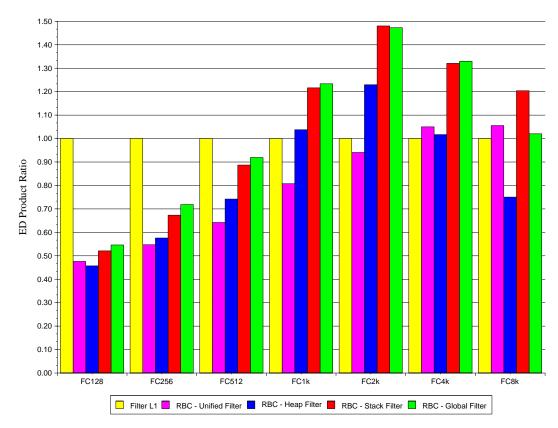

| 4.14   | Power Reduction of a Combined Filter Cache with Region-based Cachelets (Baseline:                          |    |

|        | S4k-G4k-32K with a 512KB L2 = 1.0)                                                                         | 42 |

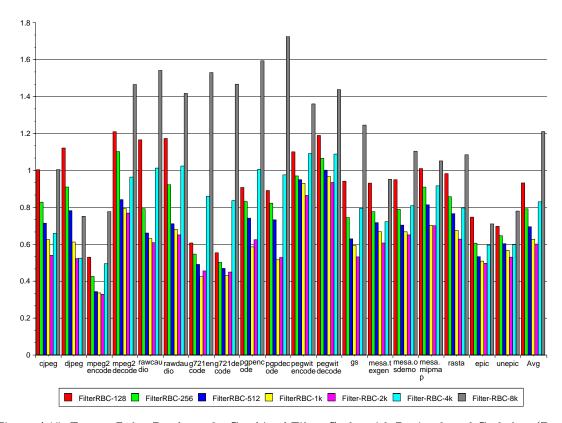

| 4.15             | Energy-Delay Product of a Combined Filter Cache with Region-based Cachelets (Baseline: S4k-G4k-32K with a $512KB L2 = 1.0$ ) | 43  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

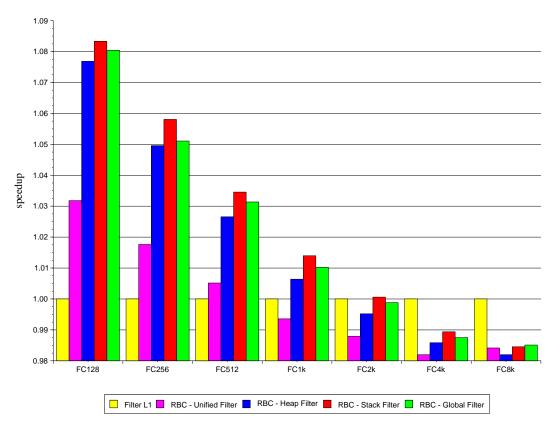

| 4.16             | Filtered L1 Cache versus Filtered Region-based Cachelets                                                                     | 43  |

|                  | Performance Speedup of a Filter Cache with Region-based Cachelets versus a Filter                                            |     |

| •                | Cache with a Conventional Cache                                                                                              | 44  |

| 4.18             | Power Comparison of a Filter Cache with and without Region-based Cachelets                                                   | 45  |

|                  | Energy-Delay Product Comparison of a Filter Cache with and without Region-based                                              |     |

|                  | Cachelets                                                                                                                    | 46  |

| 4.20             | Performance Speedup of Dedicated Region Filter Caches                                                                        | 47  |

|                  | Power Comparison of Dedicated Region Filter Caches                                                                           | 47  |

| 4.22             | Energy-Delay Product Comparison of Dedicated Region Filter Caches                                                            | 48  |

| 5.1              | Run-time Memory Access Distribution by Access Methods for SPECint2000                                                        | 51  |

| 5.2              | Cache Footprint of References by Regions (197.parser)                                                                        | 53  |

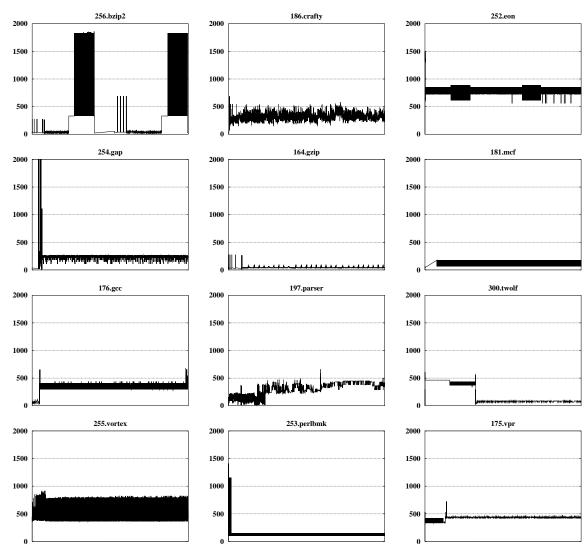

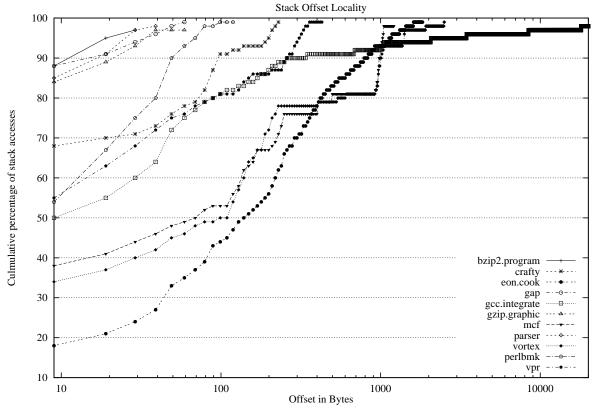

| 5.3              | Stack Depth Variations                                                                                                       | 54  |

| 5.4              | Offset Locality within Functions                                                                                             | 56  |

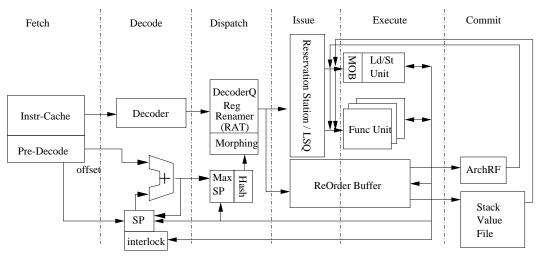

| 5.5              | Microarchitecture Extension with a Stack Value File Implementation                                                           | 57  |

| 5.6              | Load Squashing Scenario and its Optimization                                                                                 | 59  |

| 5.7              | Speedup Potentials of Morphing All Stack Accesses to Register Moves (single-ported                                           |     |

|                  | cache)                                                                                                                       | 62  |

| 5.8              | Speedup Potentials of Morphing All Stack Accesses to Register Moves (dual-ported                                             |     |

|                  | cache)                                                                                                                       | 63  |

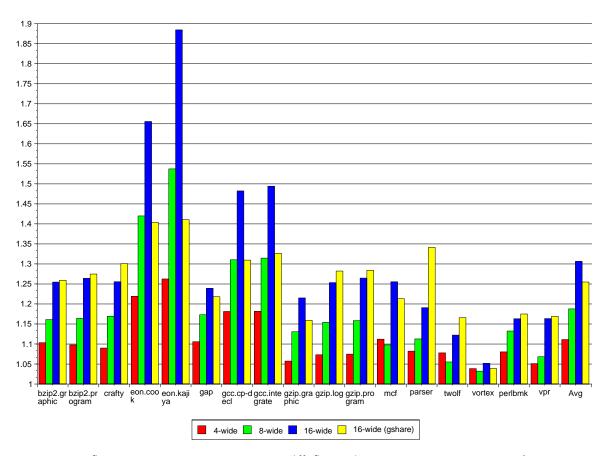

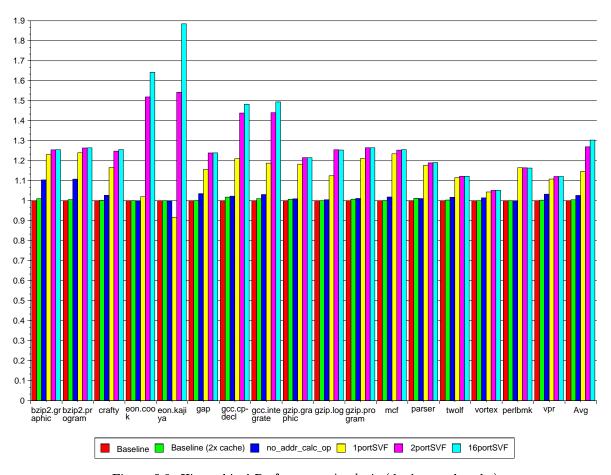

| 5.9              | Hierarchical Performance Analysis (dual-ported cache)                                                                        | 64  |

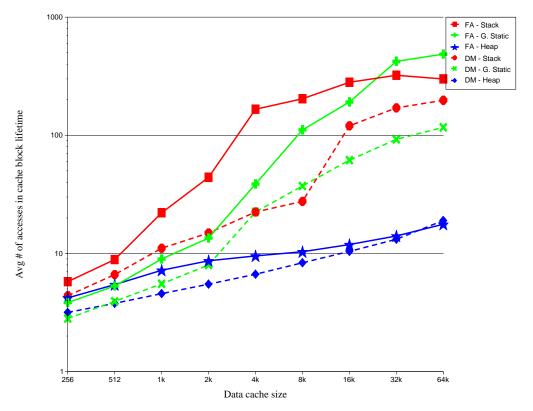

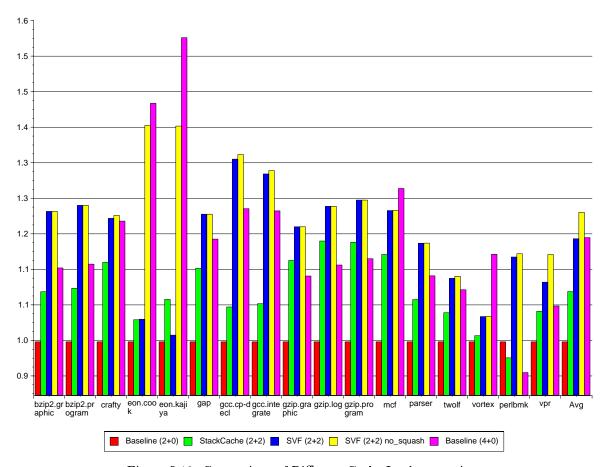

|                  | Comparison of Different Cache Implementations                                                                                | 65  |

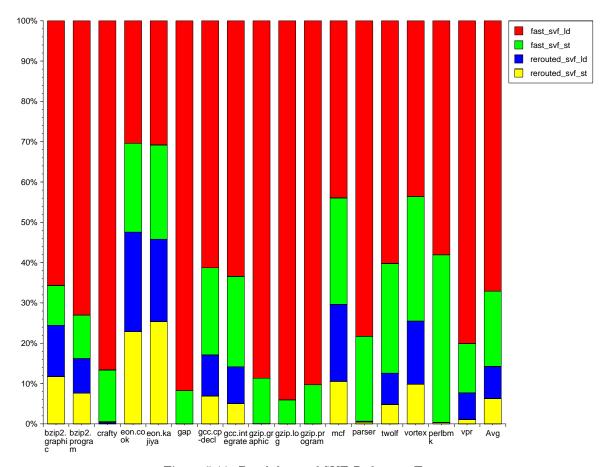

|                  | Breakdown of SVF Reference Types                                                                                             | 66  |

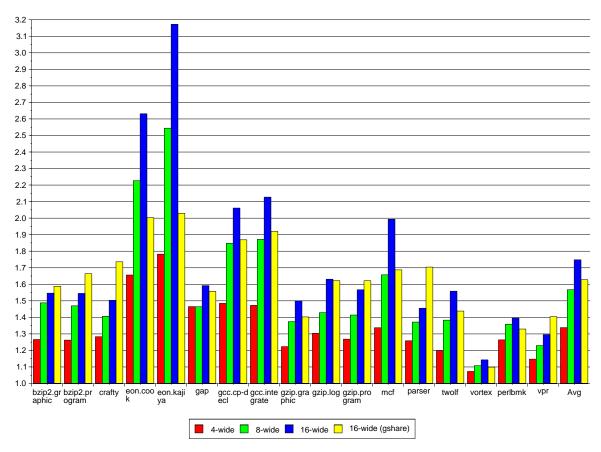

|                  | Performance Improvements over Baseline Microarchitecture                                                                     | 70  |

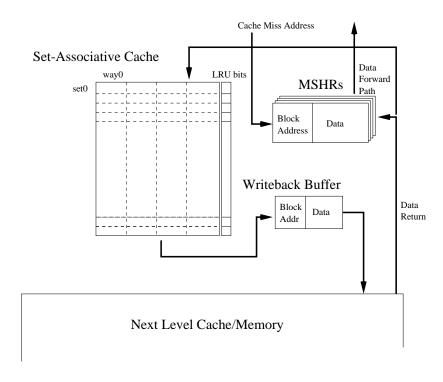

| 6.1              | Architectural Block Diagram of non-blocking caches                                                                           | 74  |

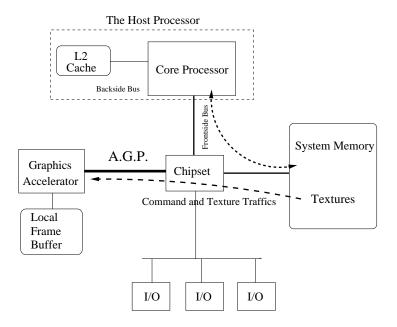

| 6.2              | A PC system architecture with AGP                                                                                            | 75  |

| 6.3              | Extra traffic by triggering writeback upon different usage states for L1 and L2 caches                                       |     |

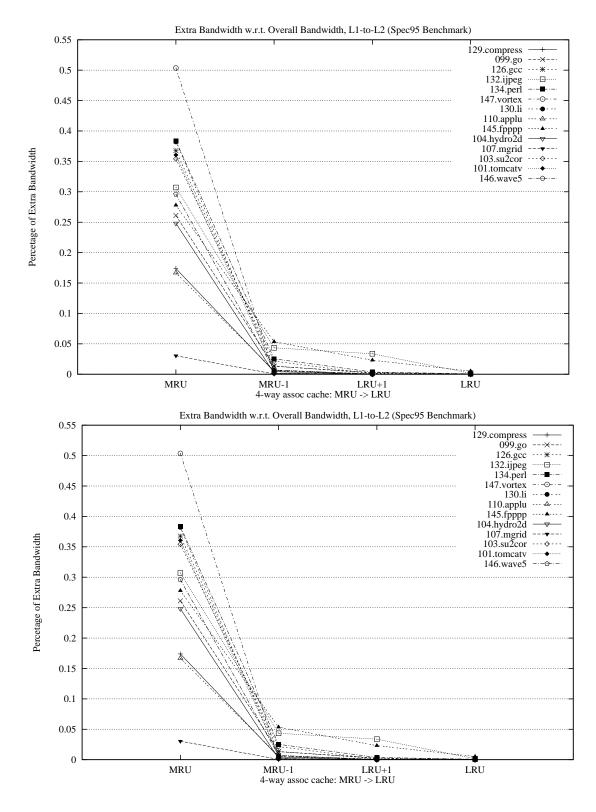

|                  | (SPEC95)                                                                                                                     | 77  |

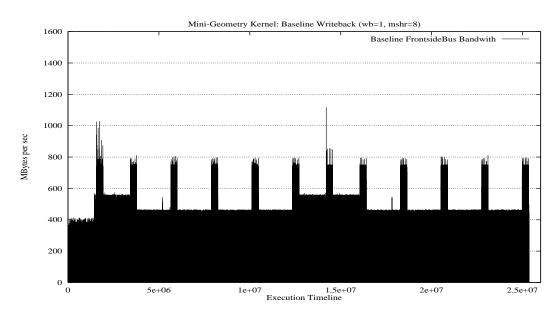

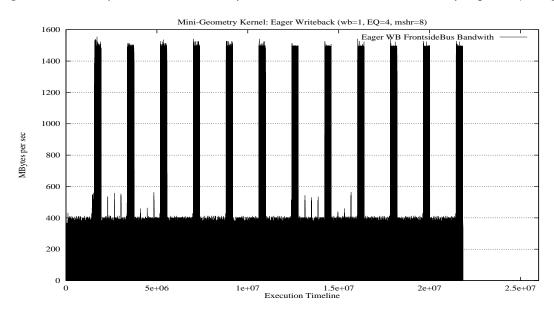

| 6.4              | Memory Bandwidth Profile by Baseline Writeback for 3D Geometry Pipeline (No light)                                           | 82  |

| 6.5              | Memory Bandwidth Profile by Eager Writeback for 3D Geometry Pipeline (No light)                                              | 82  |

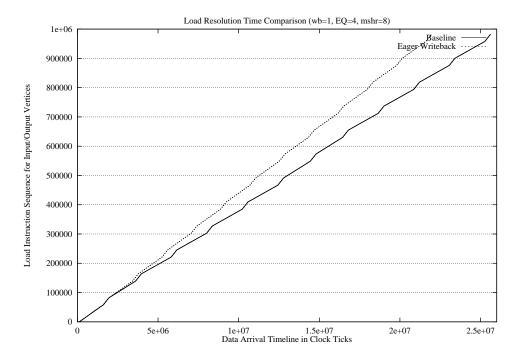

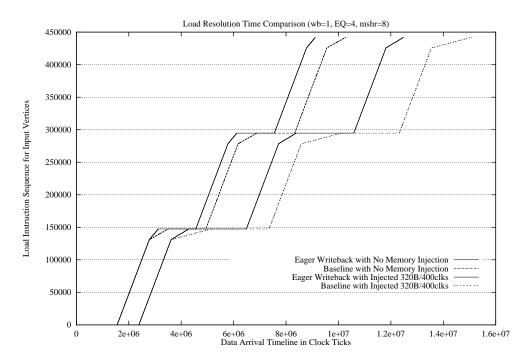

| 6.6              | Load Response Time for Input Vertex in 3D Geometry Pipeline                                                                  | 83  |

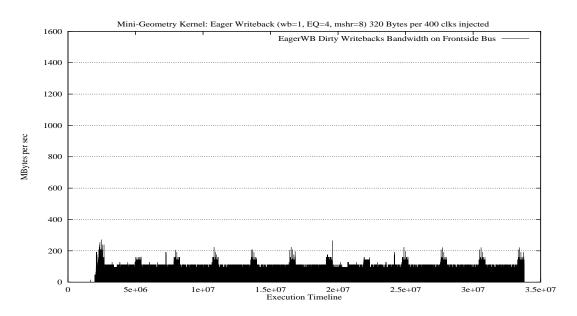

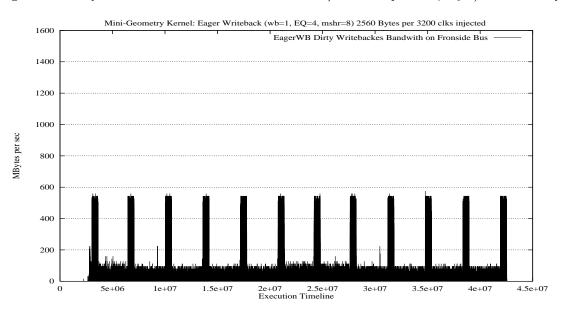

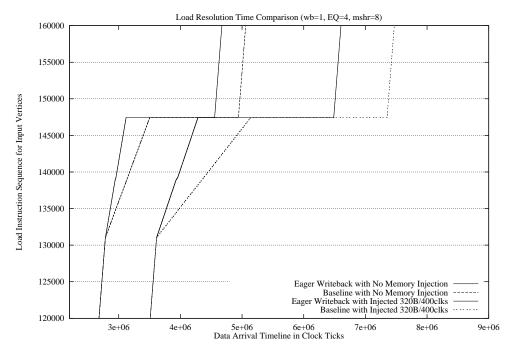

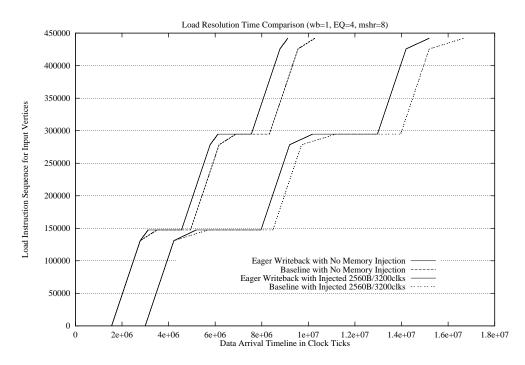

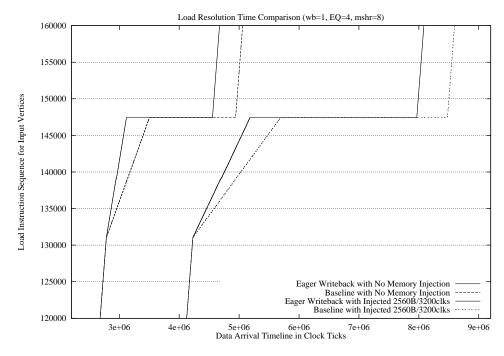

| 6.7              | Dirty WB L2-to-Mem Bandwidth with 320B/400clks Injection (Eager) for Geometry                                                | 85  |

| 6.8              | Dirty WB L2-to-Mem Bandwidth with 2560B/3200clks Injection (Eager) for Geometry                                              |     |

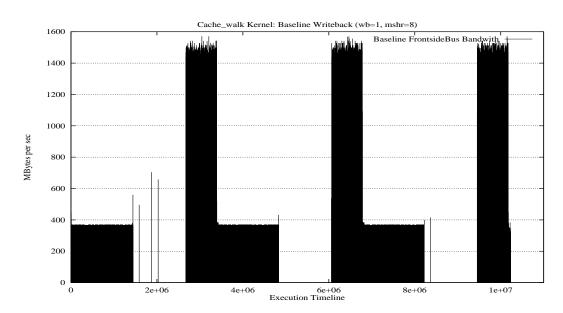

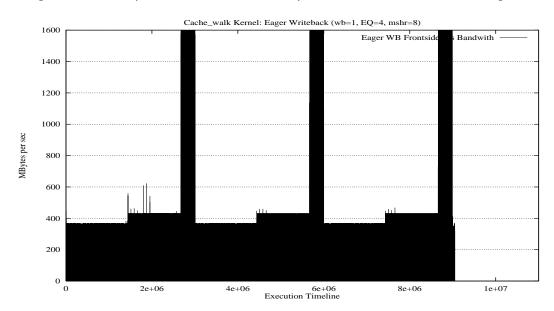

| 6.9              | Memory Bandwidth Distribution by Baseline Writeback for Streaming Kernel                                                     | 86  |

|                  | · · ·                                                                                                                        | 86  |

|                  | Load Response Time for Data Reads in Streaming Kernel (Higher Frequency Injection)                                           | 88  |

| b.12             | Zoom-In of the Load Response Time for Data Reads in Streaming Kernel (Higher                                                 | 0.0 |

| C 10             | Frequency Injection)                                                                                                         | 88  |

|                  | Load Response Time for Data Reads in Streaming Kernel (Lower Frequency Injection)                                            | 89  |

| v.1 <del>4</del> | Zoom-In of the Load Response Time for Data Reads in Streaming Kernel (Lower Frequency Injection)                             | 89  |

|                  |                                                                                                                              | UJ  |

# LIST OF TABLES

| Table |                                                                                |    |

|-------|--------------------------------------------------------------------------------|----|

| 2.1   | SPEC CPU95 benchmark                                                           | 5  |

| 2.2   | SPEC CPU2000 benchmark                                                         | 6  |

| 2.3   | Mediabench benchmark                                                           | 6  |

| 2.4   | X benchmark                                                                    | 7  |

| 4.1   | Energy-Delay Product for Mediabench with Different Region-based Cachelets      | 38 |

| 5.1   | Processor Models.                                                              | 61 |

| 5.2   | Memory Traffic for Stack Cache and SVF schemes (2KB)                           | 67 |

| 5.3   | Memory Traffic for Stack Cache and SVF schemes (4KB)                           | 67 |

| 5.4   | Memory Traffic for Stack Cache and SVF schemes (8KB)                           | 68 |

| 5.5   | Memory Traffic on Context Switches                                             | 69 |

| 6.1   | Summary of the Baseline Processor Model                                        | 78 |

| 6.2   | Latency Table (in core cycles) of the Baseline Processor                       | 79 |

| 6.3   | Performance of SPEC95 Benchmarks. (WB buffer $= 1$ , EQ $= 4$ )                | 80 |

| 6.4   | Simulated cycles of 3D Geometry Pipeline.                                      | 80 |

| 6.5   | Resource Hazard Improvement of 3D Geometry Pipeline                            | 81 |

| 6.6   | Memory Traffic Injection to 3D Geometry Pipeline. (Eager Queue = 4)            | 83 |

| 6.7   | Simulated cycles of Streaming Kernel                                           | 84 |

| 6.8   | Resource Constraint Improvement of Streaming Kernel. (Writeback buffer $= 1$ ) | 85 |

| 6.9   | Memory Traffic Injection to Streaming Kernel. (Eager Queue = 4)                | 87 |

# LIST OF APPENDICES

####

# CHAPTER 1

## INTRODUCTION

Following the rapid progression and innovation in the semiconductor industry, the microprocessor market is gradually converging into two major segments: The first segment is driven by traditional high-performance microprocessors used in information servers, scientific computation, simulation-based engineering and ever complicated content-rich multimedia and graphics-oriented applications. The second segment is growing from the emerging application market in embedded and special purpose processors, e.g. digital signal processing (DSP) processors. These processors are omnipresent in our daily life, from mobile computers, personal digital assistants (PDA), multi-purpose handsets, tablet computers, etc., to invisible microcontrollers embedded in household appliances. The design focuses of this processor category are faster design cycle for time-to-market, low energy consumption, more constrained die area budget, and flexible integration capability, all while achieving reasonable performance, making them much different from a traditional high-performance processor design.

Processor architects and researchers in the past decade have been primarily focused on the following design space: instruction level parallelism, memory level parallelism, memory throughput, and low energy designs. Evaluation metrics emphasis were also varied from cycles per instruction (CPI), instructions per cycle (IPC) to more recent energy-delay product (EDP), to emphasize different design goals for different market segments at different times.

Entering the 1990s, the per-transistor cost was no longer a roadblock to complex designs due to significant advancements in semiconductor manufacturing and design technology, processor architects were given an enormous number of transistors on a single processor chip to devote to extracting instruction level parallelism (ILP) and enhancing the locality of memory references. Superscalar architectures and RISC design philosophy [60] were accepted as the fundamental elements for building high-performance ILP processors. In the domain of a dynamic ILP processor design, the goal is to maximize the number of instructions supplied per cycle from the front-end pipeline. Innovative microarchitectural technologies towards this end were proposed and several of them have been implemented in commercial microprocessors to provide an effective instruction supply to the execution core; these include aggressive branch predictors [81][84][104][120], trace caches [54][86][95][115], value predictors [46][79] and simultaneous multithreading [38][109]. All of these technologies aim at increasing instruction throughput at an extra hardware cost, either from a single program or from multiple concurrent program threads. In addition, new types of instructions such as predicate instructions [55][31][33], memory hint [34][96], or branch hint [33] instructions were incorporated into recent instruction set architectures. Meanwhile, several ILP limit studies [20][69][73][88][112] were published to address the limits and potential issues of inherent instruction level parallelism, primarily for integer applications that were known for their high frequency of branch instructions and scanty instruction level parallelism.

Memory subsystem designs have also been extensively studied including new cache organizations

and replacement policies for more efficient and effective instruction and data management. In the early days of single-issue processor designs, traditional caches were implemented for reducing ever higher memory latency. Non-blocking caches were later proposed in [67] to increase execution concurrency of the instructions that are independent of in-flight cache misses. As the deviation between processor core speed and DRAM speed increases, multi-level caches are becoming increasingly popular. Today, several commercial high performance microprocessors are designed with three level caches [39][40][50][110]. Even though memory latency cannot be completely eliminated, researchers have developed intelligent hardware and software-based data prefetching mechanisms [23][26] as a means to improving memory level parallelism by latency hiding. Recently researchers have started to investigate new techniques for exploiting memory reference locality from the perspective of data temporality, through hardware and/or software modifications. Techniques proposed in [49][61][93] classify data based on their temporality of prior reference patterns and then deposit data of different characteristics into distinct cache/memory structures. Throughout this dynamic classification, these techniques are able to alleviate the effects of conflict misses and improve hit ratios by preferentially retaining temporal data, i.e. data exhibiting greater likelihood of reuse, in the main cache. Several software techniques were also proposed to improve data layout. They usually rely on statistics of program profiling or affinity region information provided by programmers to re-structure data in virtual memory space. Based on this information, compilers can generate a data layout with better reference locality. For example, cache-conscious data placement, proposed in [22], profiles run-time data affinity for a program and then rearranges data at linker time to achieve better reference locality. Similarly, array grouping techniques [100] mitigate local cache misses and interprocessor communication latency by packing non-consecutive references together for parallel applications.

Another major issue in the memory subsystem design is bandwidth. Most of the multimedia, telecommunication and future emerging applications stream a large amount of data to/from memory. Network-centric applications are essentially bandwidth-bound. These data streams can easily saturate memory bus bandwidth. These new applications are the major driving force behind developing novel high memory bandwidth techniques. The Accelerated Graphics Port (AGP) [29] was proposed for desktop processors to enhance the memory bandwidth between system memory and a graphics processor, primarily for delivering graphics commands and texture bitmaps. High bandwidth Rambus DRAM (RDRAM) [36], Synchronous-Link DRAM (SLDRAM) [57] and Double Data Rate DRAM (DDR-DRAM) are now accepted as new industry standards for future system main memory devices. Given a fixed amount of memory bandwidth, architects can also potentially improve system performance through more intelligent bandwidth management mechanisms that lead to more effective bandwidth utilization.

The philosophy of this dissertation is to address these design issues (energy consumption, high performance and high memory bandwidth) by analyzing and exploiting characteristics of data memory reference streams. By examining these characteristics, we propose architectural solutions to attack each problem individually. In the first part of this dissertation, we present an in-depth characterization of data memory references, including analysis of semantic region references and behavior of data stores. The first part of the analysis leads to two new cache structures designed to exploit the characteristics of high-level programming language semantics which, by convention, partitions run-time code and data into multiple separate virtual memory regions. The Region-based Cachelets design, our first novel cache architecture, is capable of improving memory performance of embedded applications while significantly reducing dynamic energy consumption. The second technique, the Stack Value File, can increase the performance of general purpose applications by routing stack data references to a separate register file-like storage structure optimized for the unique characteristics of the stack reference substream. This technique can increase memory level parallelism, reduce memory latency, and reduce off-chip memory activity. Then, we analyze the data reference behavior in a set-associative cache for data streaming applications. We present a novel technique called Eager

Writeback that effectively exploits the data reference features and improves the system performance by shifting dirty cache line writebacks and balancing memory bandwidth accordingly.

# 1.1 Contributions

This dissertation makes the following key contributions:

- 1. It investigates data memory reference behavior through the partitioning provided by programming language semantics [74]. The resulting characterization and its in-depth analysis quantitatively demonstrate the information content carried in memory address streams for each data region.

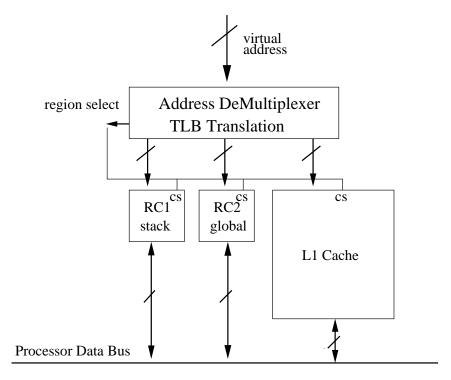

- 2. It applies the characterization methodology to some emerging media and communication applications. Based on the stack and global data memory reference characteristics, a new design concept called Region-based Cachelets [76] is proposed for low-energy embedded processor designs. This new design scheme physically divides the data cache into parallel cachelets based on the regions defined by high-level programming languages. We show that the region-based cachelet design can reduce power consumption substantially without compromising execution performance for embedded processors.

- 3. It examines the memory performance impact of programming language semantics and addressing modes. A new technique, called *Stack Value File (SVF)* [75] is proposed that uses a directly indexed circular register file effectively exploit the unique characteristics shown in stack memory reference stream.

- 4. It presents an Eager Writeback cache [77] for alleviating memory bandwidth constraints based on our analysis of data cache replacement streams in a set-associative cache. Eager Writeback is a modified writeback cache replacement scheme for achieving more effective utilization of memory bandwidth, thereby improving system performance for today's memory bound applications.

# 1.2 Organization

This dissertation is organized as follows. First, the simulation infrastructure and benchmarks used throughout this dissertation are described in Chapter 2. Chapter 3 discusses the distinct reference characteristics demonstrated in each data memory region for these applications. Additionally, we present some observations on dirty writeback behavior in graphics and data streaming applications. Chapter 4 overviews the dynamic power/energy dissipation issues on caches. Through data region characterization for media and communication benchmarks, we achieve power savings by re-organizing the first level cache into variable sized region cachelets that can more efficiently exploit the memory reference characteristics produced by programming language semantics. Chapter 5 describes the Stack Value File design for high performance processors. This technique exploits stack reference characteristics to increase memory level parallelism. Chapter 6 presents the Eager Writeback technique for improving memory bandwidth utilization and thereby improving system performance. Chapter 7 concludes this dissertation and discusses future research directions.

# CHAPTER 2

# EXPERIMENTAL FRAMEWORK

This chapter describes the experimental framework used throughout this dissertation, including our baseline processor simulator and benchmark suites. The detailed simulation models used in each individual study (such as new microarchitectural additions, instruction set architecture, machine issue width, cache configuration, memory subsystem modeling, etc.) will be detailed in each corresponding chapter.

## 2.1 Processor Simulator and Tool Suites

The infrastructure of our simulation environment used throughout this dissertation is based on the SimpleScalar tool set originally developed at the University of Wisconsin at Madison [19]. SimpleScalar was implemented to be a portable and extensible tool for microarchitecture research. This tool set includes a processor simulator and several modified GNU tools and utilities including a qcc-based compiler that is capable of generating target binary to run on the SimpleScalar instruction set architecture, or the SimpleScalar Portable ISA (PISA). The PISA encoding and addressing modes are almost identical to the MIPS ISA [64]. The processor simulator is able to simulate both the Compag Alpha ISA [102] and PISA. The processor simulator is an execution-driven simulator. Besides functional simulation and cache simulation, the simulator is also capable of simulating a dynamic ILP processor with speculative and out-of-order execution support. For dynamic scheduling machine simulation, the simulator models a Register Update Unit (RUU) that combines the functions of reservation stations (RS) and the re-order buffer (ROB) necessary for supporting out-of-order execution. An in-depth description of the RUU mechanism is in [105]. All in-flight instructions are allocated inside the RUU that maintains correct data flow between dependent instructions. Functional unit binding, instruction dispatch, data dependency resolution and retirement are all managed by the RUU. Once an instruction is ready to be committed, it is removed from the RUU and retired into the architecture state.

In this dissertation, we also study the aspects related to dynamic power dissipation in Chapter 4. The power dissipation modeling and projection is based on another tool called *Wattch* developed at Princeton University [18]. *Wattch*, an add-on extension to the original *Simplescalar* simulator, provides performance simulation as well as both static and dynamic power projection through running a single-pass of the microarchitecture-level simulation.

| Benchmark    | Source  | Application                          |

|--------------|---------|--------------------------------------|

| 099.go       | С       | Go chess game                        |

| 124.m88ksim  | С       | MC88100 chip simulator               |

| 126.gcc      | С       | GNU c compiler 2.5.3                 |

| 129.compress | С       | UNIX compression utility             |

| 130.li       | С       | Xlisp interpreter                    |

| 132.ijpeg    | С       | Image compression/decompression      |

| 134.perl     | C       | Perl interpreter                     |

| 147.vortex   | С       | Object-oriented database             |

| 101.tomcatv  | FORTRAN | Vectorized mesh generation           |

| 102.swim     | FORTRAN | Shallow water equation               |

| 103.su2cor   | FORTRAN | Monte-Carlo method                   |

| 104.hydro2d  | FORTRAN | Navier Stokes equation               |

| 107.mgrid    | FORTRAN | 3D potential field                   |

| 110.applu    | FORTRAN | Partial differential equation        |

| 125.turb3d   | FORTRAN | Turbulence modeling                  |

| 141.apsi     | FORTRAN | Weather prediction                   |

| 145.fpppp    | FORTRAN | Gaussian series of quantum chemistry |

| 146.wave5    | FORTRAN | Maxwell's equations                  |

Table 2.1: SPEC CPU95 benchmark

# 2.2 Benchmarks

#### 2.2.1 SPEC

The SPEC benchmark suites are published by the Standard Performance Evaluation Corporation, a non-profit consortium whose members include researchers, industrial hardware vendors and software vendors. The main purpose of this benchmark is to provide a common basis for characterizing the performance of different workstation-level microprocessors. High performance computer industries typically use SPEC numbers as the major indicator to quantify their machine performance and compare performance with machines from different vendors. For a processor under development, architects project and publish the SPEC target performance numbers in order to demonstrate the performance objective as well as evaluate and justify their new machine design. Every 3 to 5 years, the SPEC consortium will revise the benchmark contents to reflect a more representative collection for the state-of-the-art applications.

The SPEC CPU95 (SPEC95) benchmark suite [37] has been widely used by researchers and architects for the last five years. In some of our earlier research work in this dissertation, we performed the simulations using SPEC95 benchmark. The SPEC95 binaries used in this dissertation were compiled using the SimpleScalar GCC compiler that generates code in the PISA format. Table 2.1 describes each benchmark program. The SPEC CPU95 benchmark was retired at July, 2000.

The SPEC CPU2000 benchmark [53] is the most recently published SPEC benchmark as the successor of the retired SPEC CPU95 benchmark. We primarily use their integer benchmark suite to perform our research for studying high performance processors that are not targeted for scientific computing. The binaries of the SPEC CPU2000 benchmark used in this dissertation were compiled using the Compaq Alpha compiler with optimization level 3 and automatic loop unrolling enabled. The input files for our experiments are either taken from reference input set or training input set as explained inside the chapters. Table 2.2 describes the attributes of each benchmark program.

#### 2.2.2 Mediabench

The Mediabench benchmark suite was collected and bundled by researchers at the University of California at Los Angeles [72]. Mediabench was designed for bridging the gap among the compiler community, embedded processor architects and embedded software developers. The programs from

| Benchmark    | Source     | Application                                    |

|--------------|------------|------------------------------------------------|

| 164.gzip     | С          | Compression                                    |

| 175.vpr      | С          | FPGA circuit placement and routing             |

| 176.gcc      | С          | C programming language compiler                |

| 181.mcf      | С          | Combinatorial optimization                     |

| 186.crafty   | С          | Game playing: chess                            |

| 197.parser   | C          | Word processing                                |

| 252.eon      | C++        | Computer visualization                         |

| 253.perlbmk  | С          | PERL programming language                      |

| 254.gap      | С          | Group theory, interpreter                      |

| 255.vortex   | С          | Object-oriented database                       |

| 256.bzip2    | С          | $\operatorname{Compression}$                   |

| 300.twolf    | С          | Place and route simulator                      |

| 168.wupwise  | FORTRAN 77 | Quantum chromodynamics                         |

| 171.swim     | FORTRAN 77 | Shallow water modeling                         |

| 172.mgrid    | FORTRAN 77 | Multi-grid solver                              |

| 173.applu    | FORTRAN 77 | Parabolic/Elliptic PDEs                        |

| 177.mesa     | С          | 3D OpenGL graphics library                     |

| 178.galgel   | FORTRAN 90 | Computational fluid dynamics                   |

| 179.art      | С          | Image recognition / Neural networks            |

| 183.equake   | C          | Seismic wave propagation simulation            |

| 187.facerec  | FORTRAN 90 | Image processing: face recognition             |

| 188.ammp     | C          | Computational chemistry                        |

| 189.lucas    | FORTRAN 90 | Number theory / primality testing              |

| 191.fma3d    | FORTRAN 90 | Finite-element crash simulation                |

| 200.sixtrack | FORTRAN 77 | High energy nuclear physics accelerator design |

| 301.apsi     | FORTRAN 77 | Meteorology: pollutant distribution            |

Table 2.2: SPEC CPU2000 benchmark

| Benchmark    | Application                                                     |  |

|--------------|-----------------------------------------------------------------|--|

| cjpeg        | Discrete Cosine Transform Image Compression                     |  |

| djpeg        | Discrete Cosine Transform Image Decompression                   |  |

| mpeg2encode  | MPEG2 video encoder                                             |  |

| mpeg2decode  | MPEG2 video decoder                                             |  |

| rawcaudio    | Speech compression using ADPCM standard                         |  |

| rawdaudio    | Speech decompression using ADPCM standard                       |  |

| g721encode   | Voice compression using G.721 standard                          |  |

| g721decode   | Voice decompression using G.721 standard                        |  |

| pgpencode    | Data encryption and signing using RSA, IDEA and MD5             |  |

| pgpdecode    | PGP decoding exercising RSA, IDEA and MD5                       |  |

| pegwitencode | Public key encryption and authentication                        |  |

| pegwitdecode | Public key decryption and authentication                        |  |

| gs           | Ghostscript                                                     |  |

| mesa.texgen  | Mesa 3D OpenGL library (Textured Teapot)                        |  |

| mesa.osdemo  | Mesa 3D OpenGL library (Draw Polygons with Z-buffering)         |  |

| mesa.mipmap  | Mesa 3D OpenGL library (Texture mapping)                        |  |

| rasta        | Speech recognition                                              |  |

| epic         | Data compression using wavelet decomposition and Hoffman coding |  |

| unepic       | Epic decoding wavelets and Huffman coding                       |  |

Table 2.3: Mediabench benchmark

| Benchmark | Application                              |

|-----------|------------------------------------------|

| Doom      | 3D shoot'em-all game                     |

| POVray    | Persistence of Vision Ray-Tracer         |

| xanim     | Multiformat animation/video/audio viewer |

| xlock     | X-window screen saver                    |

Table 2.4: X benchmark

the Mediabench benchmark suite represent the workloads for a variety of emerging multimedia and communication applications. These applications are also recognized as the application software and algorithms commonly used in personal telecommunication, mobile and PDA devices. Table 2.3 describes the algorithm for each application.

The binaries were compiled using the SimpleScalar *gcc* compiler in PISA format. The optimization level 3 and automatic loop unrolling were turned on in the compilation.

## 2.2.3 X Benchmark

The X benchmark suite was collected by Todd Austin [98]. It consists of four applications representing different graphics algorithms as listed in Table 2.4. *DOOM*, a popular video game developed by *id software* corporation, uses a polygon-based rendering algorithm. *POVray* is a public domain ray tracing package developed for generating photo-realistic images on a computer. The third application *xanim* is an animation viewer which processes an MPEG-1 data stream to display an animated sequence. The final application, *xlock*, a popular X-window screen saver, renders a 3D polygonal object on the screen.

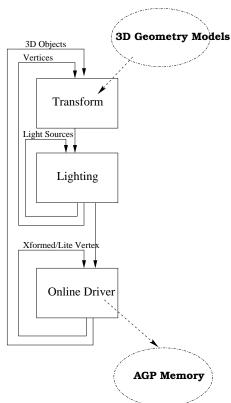

# 2.2.4 3D Geometry Pipeline

Today's polygon-based 3D graphics engine is composed of two major components, a 3D geometry processing pipeline and a rasterization pipeline. The 3D geometry processing pipeline as shown in Figure 2.1 is representative of a very frequently used algorithm in most polygon-based rendering engines. 3D geometry processing, consisting of intensive floating-point operations on a large quantity of vertex data from memory, handles vertices from the object model database. It maps the vertices from the world coordinate space to viewer's space, i.e. the display. It also computes the interaction between the light sources and their effect on each vertex for generating the shading intensity to be used during rasterization. These functions are typically done on the host processor. Once the vertices are transformed and lit, they are sent to the rasterization pipeline for scan-converting them into pixels on the display. The rasterization pipeline interpolates color values for each interior pixel within a polygon. Rasterization is typically performed by a dedicated graphics accelerator.

This pipeline consists of three nested loops wrapped by two outer loops which iterate through frames and 3D objects in the world space. The first innermost loop processes vertices for each 3D object assuming the entire object is modeled by a single triangle strip or a triangle fan. A triangle strip or fan as illustrated in Figure 2.2 is an object representation using a pre-ordered triangulation scheme. It is supported by popular graphics libraries such as OpenGL [118]. Using such an ordering, only one incremental vertex needs to be specified to describe a new triangle. For example, T1 is constructed by V1, V2 and V3. T2 is constructed by V2, V3 and V4. It is a more compact representation, therefore it requires fewer number of operations performed in the geometry pipeline. The basic functionality performed inside the innermost loop includes transformation, lighting, and command output. Figure 2.3 illustrates the control flow chart in block diagrams.

The transformation function projects the new location of each vertex on screen through a 4x4 matrix multiplication and a viewport transformation. The lighting function calculates the interaction

```

MINI-GEOMETRY()

while (frames)

for (objects in each frame)

for (every 4 vertices)

/* Transformation */

\begin{array}{l} tx = m11*InV[]_x + m21*InV[]_y + m31*InV[]_z + m41; \\ ty = m12*InV[]_x + m22*InV[]_y + m32*InV[]_z + m42; \\ tz = m13*InV[]_x + m23*InV[]_y + m33*InV[]_z + m43; \end{array}

w = m14 * InV[]_x + m24 * InV[]_y + m34 * InV[]_z + m44;

OutV[]_{rw} = 1/\tilde{w};

OutV[]_{tx} = X_{offset} + tx * OutV[]_{rw};

\begin{array}{l} OutV[]_{ty} = Y_{offset} + ty * OutV[]_{rw}; \\ OutV[]_{tz} = tz * OutV[]_{rw}; \end{array}

* Texture coordinates copying */

OutV[]_{tu} = InV[]_u;

OutV[]_{tv} = InV[]_v;

* Lighting Loop

ID_r = ID_g = ID_b = 0.0;

for ( every light source )

dot = LDir[]_x * InV[]_{nx} + LDir[]_y * InV[]_{ny} + LDir[]_z * InV[]_{nz};

ID_r = ID_r + Ambient_r + Diffuse_r * dot;

ID_g = ID_g + Ambient_g + Diffuse_g * dot;

ID_b = ID_b + Ambient_b + Diffuse_b * dot;

OutV[]_{cd} = ((int)ID_r << 24)|((int)ID_g << 16)|((int)ID_b << 8|\alpha);

* Device driver loop */

for ( each transformed and lit vertex )

* Assume Tri-Strip triangles */

/* Copy entire OutV records to graphics AGP memory */

GfxCommand[vertex - 2] = OutV[vertex - 2];

if(even - numbered vertex)

GfxCommand[vertex] = OutV[vertex];

GfxCommand[vertex-1] = OutV[vertex-1];

GfxCommand[vertex - 1] = OutV[vertex - 1]:

GfxCommand[vertex] = OutV[vertex];

```

Figure 2.1: Algorithm of the mini-geometry kernel

of each vertex with light sources and generates the color intensity for each vertex. This calculation involves a dot product between the light direction vector and the vertex normal vector using a Phong illumination model [113]. A single parallel light source with diffuse only components is assumed in the lighting model. For a parallel light source, per-vertex normal transformations can be replaced by an inverse transformation of the light source location on a per-scene basis, thus eliminating a large number of computations for generating light direction vector of each vertex. A color packing conversion then packs four single-precision floating-point RGBA color intensities into a packed 4-byte integer. The instruction set architecture of interest is assumed to support four wide SIMD computation, similar to Intel's Pentium III Processor.

After finishing with all the vertices in one object, a loop imitating the functionality of a device driver is invoked (the *command output* function). This driver loop breaks one triangle strip into individual triangles and copies these transformed and lit vertices to the uncacheable and/or write-combinable graphics memory, e.g. Advanced Graphics Port memory space. We adopt the online driver model [91][121] advocated by Intel's Pentium III architects in the pipeline. It possesses the advantage to copy the post-transformed and lit vertices into graphics memory on the fly concurrently

Figure 2.3: Geometry Processing Loop Structure

overlapped with the rest of the geometry processing. There is no need for allocating extra memory space to an intermediate buffer for device driver, therefore, overall performance is improved.

# 2.2.5 Streaming Kernel

```

Streaming()

\mathbf{float}\ array_A[MAX],\ array_B[MAX];

for (m = 0; m < loop; m + +)

for ( array_A[i] \in each set of L2 cache )

write array_A[i] to way 0;

write array_A[i+1*8*set\_size] to way 1;

write array_A[i+2*8*set\_size] to way 2;

write array_A[i+3*8*set\_size] to way 3;

for (array_A[j] \in each cache line in L2 cache)

read array_A[j];

compute array_A[j]:

write array_A[m];

for (array_B[k] \in each set of L2 cache)

read array_B[k] into way 0;

read array_B[k+1*8*set\_size] into way 1;

read array_B[k + 2 * 8 * set\_size] into way 2;

read array_B[k+3*8*set\_size] into way 3;

write array A[m];

```

Figure 2.4: Algorithm of the Streaming Kernel

The algorithm of *Streaming* kernel is presented in Figure 2.4. This algorithm mimicking multimedia data streaming consists of three inner loops that exercise the L2 cache. The first loop writes data into  $array_A[]$ . The second loop reads data from  $array_A[]$ , performs some floating-point computation and passes the results to inner loop invariant array elements. Finally the third loop accesses a new array  $(array_B[])$ , displacing elements of  $array_A[]$  from the cache.

This program is designed to represent the typical behavior of many emerging streaming applications. As pointed out previously, however, in order to highlight the memory system in a uniprocessor, no actual computational work is performed per data read.

# CHAPTER 3

# MEMORY REFERENCE CHARACTERIZATION

# 3.1 Virtual Memory Space Partitioning

The run-time storage allocation of a program is conventionally subdivided into several nonoverlapped regions: the generated target code, static and dynamic data objects [2]. The mobility of data objects depends on the specification of each programming language. For example, all data objects in Fortran can be allocated statically at compilation time into pre-determined storage areas for the sizes of their data objects are static and known prior to execution. Therefore, even activation records can be allocated during program compilation. However, for languages such as C or Pascal that support data allocation under program control, the locations of these data objects are manipulated dynamically by a run-time system. These programming language semantics provide the capability for flexible data manipulation such as dynamic data object allocation and recursive procedure calls. Thus, the sizes of data structures of a program can vary as needed under different run-time scenarios. In addition, static binding of activation records can no longer be used in recursive procedural calls. Conventionally, memory references for modern microprocessors fall into the following categories — code, read-only data (literals), global static data, stack data and heap data; according to the regions of memory they access and the access method used. The stack data region is used for the dynamic allocation of activation records; the heap data region is used for dynamic data object allocation, while code (i.e. program binary), read-only data and global static data are statically allocated by the compiler and linker.

Figure 3.1: Run-time Memory Subdivision for MIPS and Compaq Alpha Architectures

Figure 3.1 illustrates the regions from virtual memory partitioning used by the MIPS architecture [64] and the Compaq Alpha architecture [16]. For the MIPS architecture, a system-defined amount of space is allocated to the stack, which grows down. The top of stack (TOS¹) dynamically maintains the size of the stack, which forms a bound on address references to the stack. The bottom address range, allocated during compilation, includes read-only data, the instruction code region and the global static data region. Memory is dynamically allocated at run-time by the program from the heap, which grows upwards from the middle address range. For both architectures, and most other architectures, newly allocated stack memory grows from higher addresses to lower addresses, thus new stack space can be typically allocated via a "push" operation; heap memory allocation grows upward.

# 3.2 Memory Reference Distribution

# 3.2.1 Distribution of Memory Instructions

The majority of data memory references fall into the stack, global static data and heap regions, although some applications that intensively use strings, constants, such as data formatting, could access read-only data quite frequently. For example, using printf() in C often access a user-defined read-only literal for the format string (first argument). To understand the memory reference behavior by region, the distributions of run-time data memory accesses were profiled using the following two benchmark suites, the latest SPEC CPU2000 integer benchmark (SPECint2000) and Mediabench benchmark, described in Section 2.2. The Compaq Alpha ISA represents a 64-bit architecture while the PISA is 32-bit. Both processors are RISC-like machines that follow the RISC philosophy of a load/store architecture. Hence, nothing but load and store instructions may access memory.

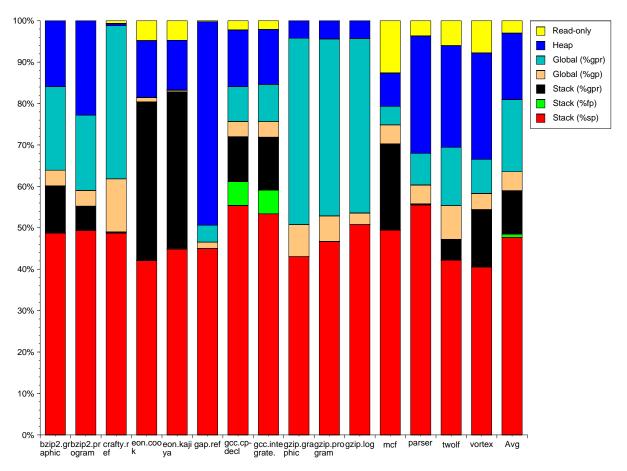

Figure 3.2 and Figure 3.3 show the profiling statistics of memory references by regions. The data in both figures are normalized to the total number of memory instructions. For the SPECint2000 profiling data, an average of 42% of the instructions executed access memory. Stack references account for an average of 56% of all memory accesses, while global static data references account for about another 21% and a majority (20%) of the remaining accesses are to the heap. Only 3% memory accesses are to the read-only data region.

A slightly different behavior from the SPECint2000, the Mediabench contains an average of 24% of the instructions accessing memory. Out of this 24% memory instructions, stack references account for an average 39.1% of all memory references, while global static data references and heap references average about 30% each of the total memory references. Data read from the read-only region are rather insignificant (about 0.1%) in Mediabench. Also note that djpeg, mpeg2encode, epic and unepic skew these averages with an extraordinarily large portion of heap accesses.

## 3.2.2 Distribution of Data Cache Occupancy

As demonstrated in the previous section, stack references account for the majority of the memory references while global static and heap data account for approximately equal proportions of the rest of the memory activities. In this section, we will quantify the cache residency behavior by using a physical data cache structure to characterize their respective occupancy ratio for each data region at run-time.

Figure 3.4, Figure 3.5, Figure 3.6, and Figure 3.7 show normalized data occupancy ratios for a direct-mapped, two-way, four-way, and eight-way set associative cache using SPECint2000 benchmark; each way of these caches consists of a 16KB content addressable memory. For instance

<sup>&</sup>lt;sup>1</sup>The TOS in this example actually maintains the *lowest* stack memory address rather than the top memory address. TOS is thus used as a conventional nomenclature in this case.

Figure 3.2: Percentage of Memory Access Regions for SPECint2000

in Figure 3.6, a four-way set associative first level cache is used in our profiling experiment. There are four stacked bars for each program of the SPEC2000int benchmark. In this figure, way0 or the Most Recently Used (MRU) cache line, is drawn in the leftmost hand side of the four bars; while way3 or the Least Recently Used (LRU) line is drawn in the rightmost side. The occupancy count for each memory region in each entry of the cache is calculated as described in the following. Each time when a data cache access is initiated, we take a snapshot for all cache ways of the set being accessed and increment the corresponding region occupancy counter for each way based on the region of the data that reside in that particular cache line entry.

For each stacked bar, we averaged the region occupancy counters across entire cache sets and normalized each counter for all four data regions: read-only, heap, global static and stack data, from top to bottom. Overall, it is observed that most of the stack data can be found in way0, i.e. the MRU state; only 4.4%, 3.0% and 2.6% of the time stack data are residing in way1, way2 and way3. Nevertheless, heap data show relatively opposite behavior from stack data. Only 20.6% of the time, heap are found in MRU state. They spent more of their lifetime in other cache ways: 73.8% for way1, 81.3% for way2, and 83.5% for way3. For some of the benchmark programs such as 186.crafty and 164.gzip, global static data occupy a longer period of time in way1, way2 and way3. This characteristics corresponds to the heavy memory references in global static data in Figure 3.2. 176.gcc also shows slightly different behavior, mainly the stack data. In most of the other benchmark programs, stack region is only heavily accessed in way0. Once after they were sent from MRU state down to less recently used ways, they were seemingly replaced out of the cache without being reaccessed temporally. For 176.gcc, however, the stack data show some temporal locality during their

Figure 3.3: Percentage of Memory Access Regions for Mediabench

lifetime in all cache ways. Approximately 30% of the time, they are found in way1, way2 and way3. As we increased the size of the cache by increasing the number of ways in the cache from Figure 3.5 to Figure 3.7, it is noticed that the heap data tend to occupy the non-MRU ways even more frequently in most of the benchmark programs. In other words, the heap data contain very little temporal locality in these integer programs.

The occupancy information collected from this characterization suggests that most of the stack data would reside in MRU states of cache lines while most of the LRU lines contain heap data. It implies that heap data are less frequently or unlikely to be promoted again to the MRU state once they have been demoted to non-MRU states. In fact, this provides some useful information for heuristics that exploit generational behavior in caches to either reduce power consumption or enhance cache hit ratio. For example, Kaxiras et al. [65] proposed a technique that reduces static leakage power by gating off supply voltage  $V_{dd}$  of the decayed cache lines, namely, those lines that are very unlikely to be reused in the near future.

# 3.3 Analysis of Regional Reference Characteristics

# 3.3.1 Weighted Reference Distance

We have shown that stack data outstrip the other data in terms of reference activity and cache occupancy. In this section, we will investigate the average cache line locality, including temporal and spatial locality, for each region. Our goal here is to understand how often each individual cache

Figure 3.4: Data Occupancy Ratios in Each Region for a Direct-Mapped 16KB Cache

line of a particular data region is re-accessed during execution. To measure the reference locality in a quantitative manner, we define and calculate the weighted reference distance for each data region. We assume that  $\Psi^n_{(R,\ell)}$  denotes the total number of memory references, accumulated from all data regions, at the time when the  $n^{th}$  memory instruction accesses cache line  $\ell$  in region R. The weighted reference distance, denoted by Dist(R) for region R is computed as follows. Given there are L cache lines accessed within the lifetime of a program, and there are  $N_\ell$  references for each cache line  $\ell$  within region R. The objective is to obtain an average distance between two successive accesses to the same cache line, for all cache lines in an infinitely large cache. As long as the memory access sequence is the same, i.e. no out-of-order effect, the only cache parameter that could change Dist(R) is the cache line size. The formula is shown below.

$$Dist(R) = \frac{\sum_{\ell=1}^{L} \sum_{n=1}^{N_{\ell}} (\Psi_{(R,\ell)}^{n} - \Psi_{(R,\ell)}^{n-1})}{\sum_{\ell=1}^{L} (N_{\ell} - 1)}$$

Figure 3.8 illustrates the weighted reference distance for each data region using SPECint2000 benchmark. The cache line size used in this experiment is 32 bytes. Note that the distance on the y-axis, represented by the number of memory references in-between 2 consecutive accesses to the same cache line, is plotted on a log scale. As the figure shows, the weighted reference distance of stack cache lines is mostly below 100 and has a harmonic mean value of 66. The only outlier is 126.gcc that exhibits a longer Dist(R), close to 10,000. In contrast, the weighted reference distance of heap cache lines shows a much greater Dist(R) for all the benchmark programs. The Dist(G) of the global static data spread in-between those of stack and heap data yet are closer to the Dist(S) of stack data.

Figure 3.5: Data Occupancy Ratios in Each Region for a 2-way 32KB Cache

The respective harmonic means of the weighted reference distance are 66, 693, 26,387, and 1,499 for stack, global static, heap and, read-only data regions. This distance can be regarded as a metric of reference locality or re-access distance for cache lines in each region under the circumstances that no replacement has ever occurred in the cache.

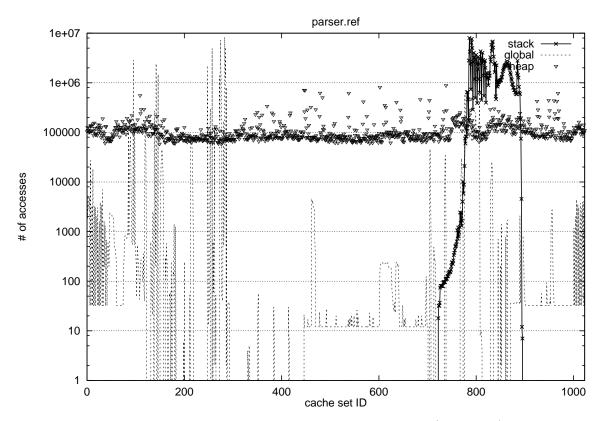

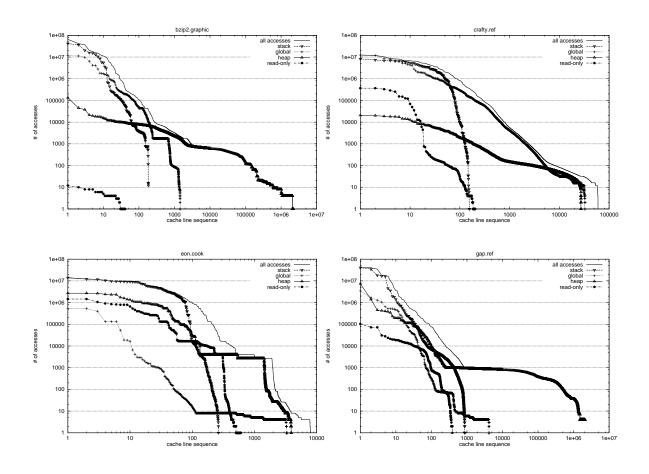

# 3.3.2 Unique Memory Block References by Region

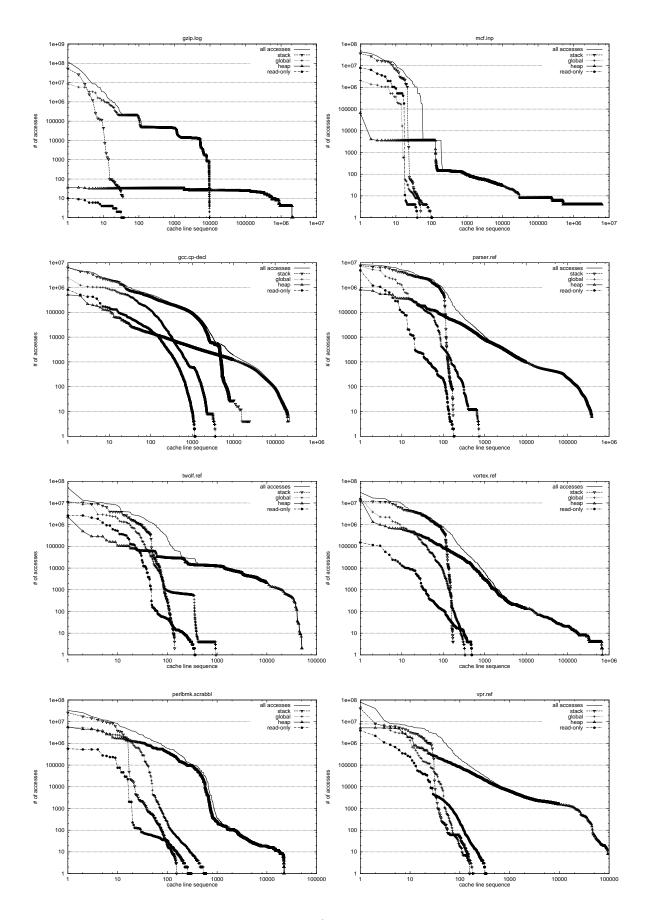

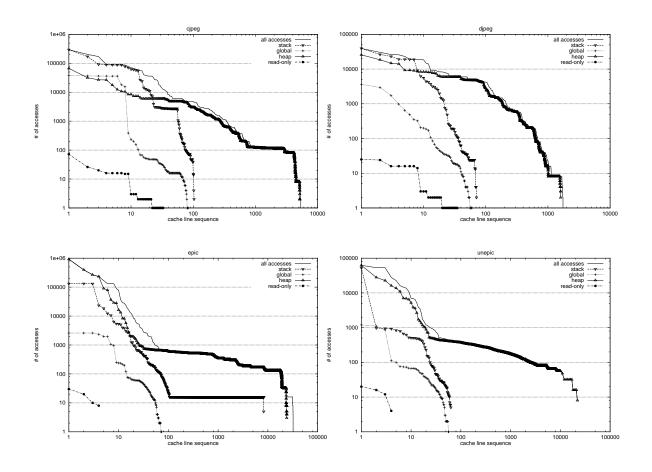

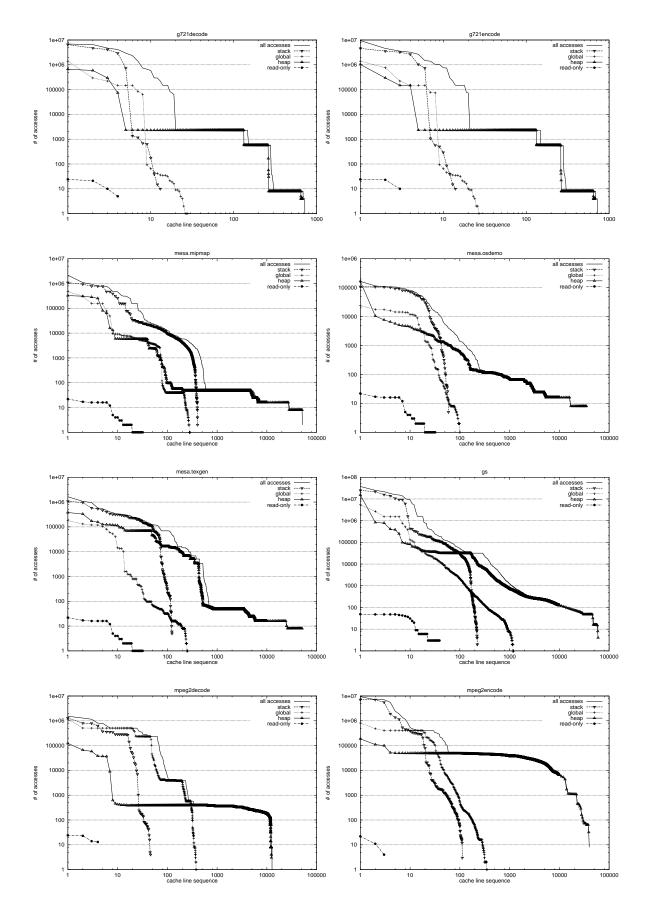

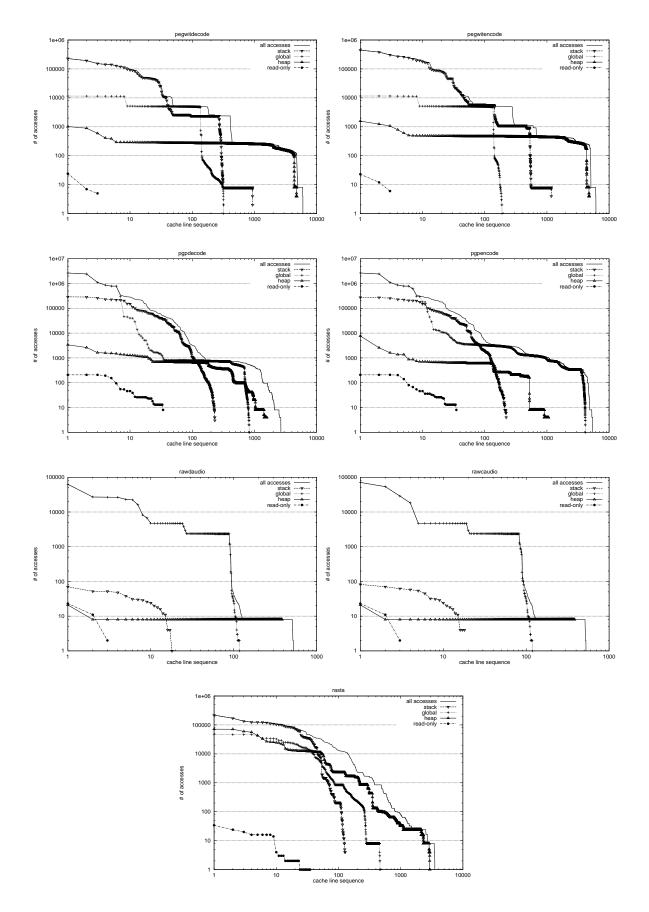

Figure 3.9 and Figure 3.10 show the unique memory block (or cache line) references by regions for 256.bzip2 and mpeg2encode respectively. The intention of this characterization is to understand the distribution of cache line accessed in each region, measured by the number of references for each unique memory block during execution. A unique memory block is essentially distinguished by the frame address of a cache line, i.e. the tag address plus the index address. All cache lines are tagged and sorted by their numbers of references. On the x-axis, each curve representing each data region is plotted on a log scale from the most referenced cache line, or the hottest cache line, starting from a unique memory block identification number 1 at the left, to the least referenced cache line. The y-axis plots the number of accesses on a log scale as well. Using Figure 3.9 as an example, the curves of stack, global static and read-only data all drop quite steeply. For instance, after the top 100 most referenced stack cache lines, the numbers of accesses to each of the rest stack cache lines are all well below 10,000 times. However, the heap cache lines demonstrate a very distinct behavior from the other regions. The trend of the heap curve follows very closely to that of the "all accesses" curve. In other words, after the top 1,000 most referenced cache lines, most of the

Figure 3.6: Data Occupancy Ratios in Each Region for a 4-way 64KB Cache

rest of the references, spread across a large number of cache lines, go to the heap. Heap data, by and large, occupy a large cache memory image at run-time. Without regard to conflict misses, it is seemingly true that architects are designing an ever larger cache for facilitating heap data. The other SPEC2000int and Mediabench applications all demonstrate a very similar trend as depicted in Appendix A and Appendix B.

#### 3.3.3 Information Content of Cache Frame Addresses

In this section, we study the information content inherent to the data references of programs written in high-level languages. Information theory [99] has been widely used to measure the information complexity of computing and communication systems. Hammerstrom and Davidson [51] developed several estimation techniques based on information theory for analyzing the information content of memory addressing. In order to understand the relative information content, or *entropy*, of data access streams for each region, we apply the fundamental concepts of information theory to the data addresses referenced, using the cache frame address as a random variable.

Let  $P(A_i)$  be the probability of a cache frame address,  $A_i$ , being referenced during a program's lifetime. The information  $I(A_i)$  carried by each  $A_i$  is then computed as  $\log_2^{\frac{1}{P(A_i)}}$ . For example, assuming that only 3 memory addresses are referenced in a program and their respective reference probabilities are  $\frac{1}{2}$ ,  $\frac{1}{4}$ , and  $\frac{1}{4}$ . Then minimum information represented by number of bits for each of these 3 addresses can be compressed and communicated by 1 bit, 2 bits and 2 bits. For a zero-

Figure 3.7: Data Occupancy Ratios in Each Region for an 8-way 128KB Cache

memory source [1] system<sup>2</sup>, the information content or entropy carried for each cache frame address is  $P(A_i) * I(A_i)$ . Therefore, the average entropy H(A, R) of each data region R is defined as:

$$H(A, R) \doteq \sum_{A_i \in R} P(A_i) * \log_2^{\frac{1}{P(A_i)}} = -\sum_{A_i \in R} P(A_i) * \log_2^{P(A_i)}$$

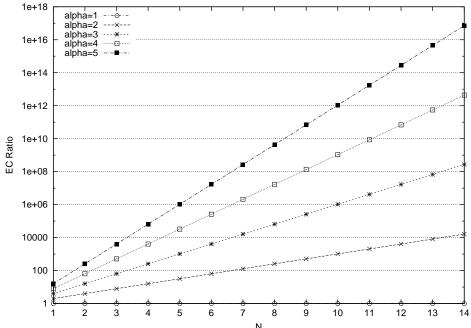

Using this equation, we calculate and plot the H(A,R) for each region R in Figure 3.11. According to prior analysis and discussion, it is expected that the entropy of heap data addresses can be much higher than those of the other regions. As shown, the average entropy H(A, Heap) is approximately 3 times higher than H(A, Stack) and H(A, Static). Namely, heap data addresses consist of much richer information than the other two major data address regions. We now discuss how this could impact the cache sizes.

Consider two discrete caches for data storage in region X and Y with their minimum cache sizes of  $C_X$  and  $C_Y$  to satisfy their data capacity. We define a metric called the *expected capacity ratio*, ECR, to be  $\frac{C_X}{C_Y}$ . The entropy H(A,R) represents the minimum number of bits needed to convey information needed for region R. Therefore, the expected capacity ratio of these two caches can be represented as follows.

$$ECR_{\frac{X}{Y}} = \frac{2^{H(A,X)}}{2^{H(A,Y)}} = 2^{(H(A,X)-H(A,Y))}$$

$<sup>^{2}</sup>$ A zero-memory source is an information system in which the successive information or symbols emitted are statistically independent.

Figure 3.8: Weighted Reference Distance of Cache Lines by Regions

Let H(A, X) of region X be a multiple  $\alpha$  (alpha) of H(A, Y) of region Y, where the size  $C_Y$  is equal to  $2^N$ . Then we can derive

$$ECR = 2^{N(\alpha-1)}$$

Figure 3.12 plots the expected capacity ratio with varied  $\alpha$  and N. For instance, when  $\alpha$  is 3 (which is approximate to what we measured in the benchmark) and assume a 1KB stack cache (i.e. N=10) can satisfy information for stack region. According to Figure 3.12, we need roughly a 1MB heap cache in order to satisfy the needed address information in heap region. Note that the y-axis in the graph uses a log scale. Thus when  $\alpha$  increases linearly, the ECR actually grows exponentially in N. That is, the effective cache size expands exponentially even if the entropy increases only linearly.